**SKYWORKS®****DATA SHEET**

## SKY62101 12-Output, Any-Frequency, Any-Output Clock Generator with Ultra-Low Jitter

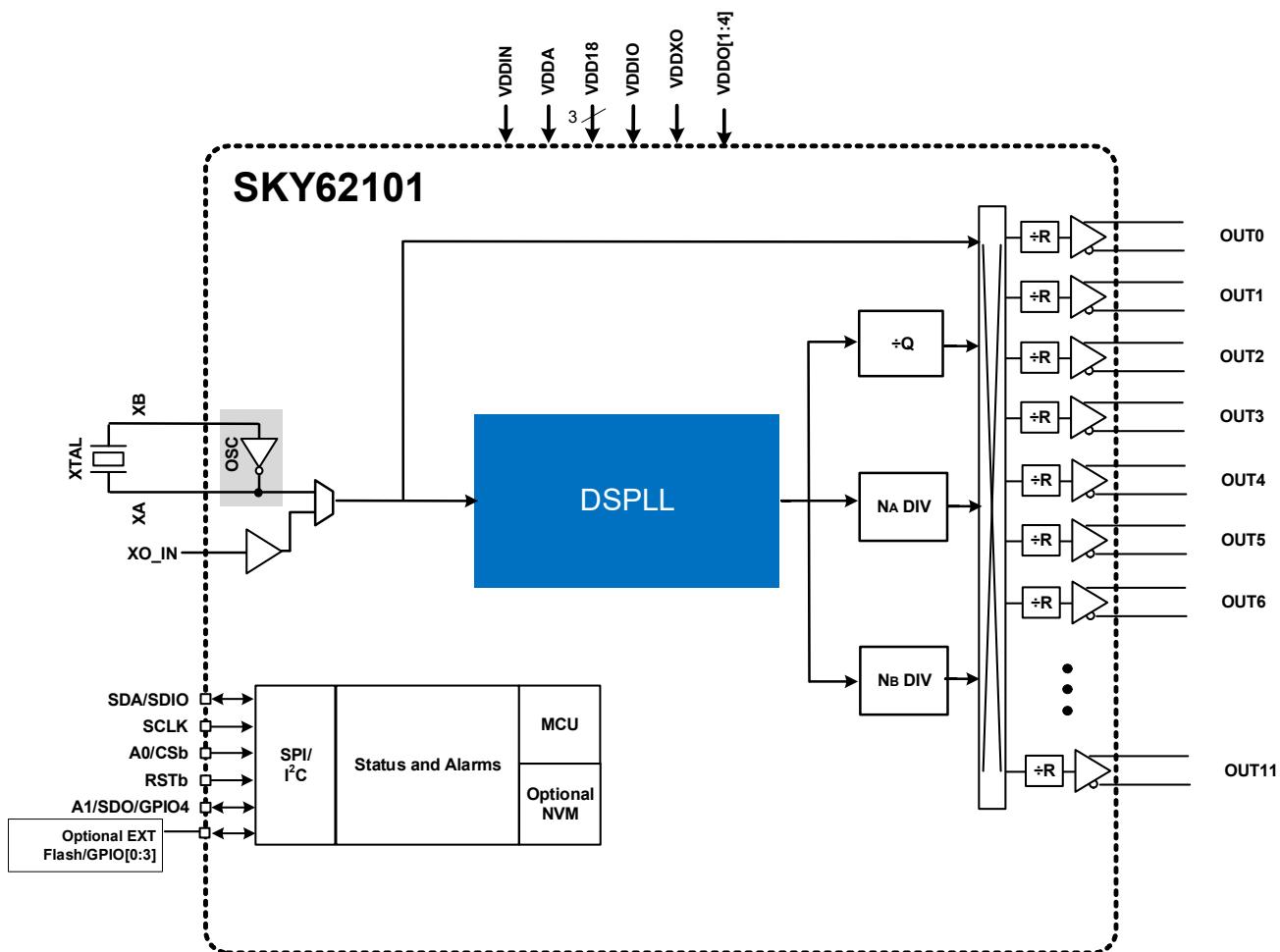

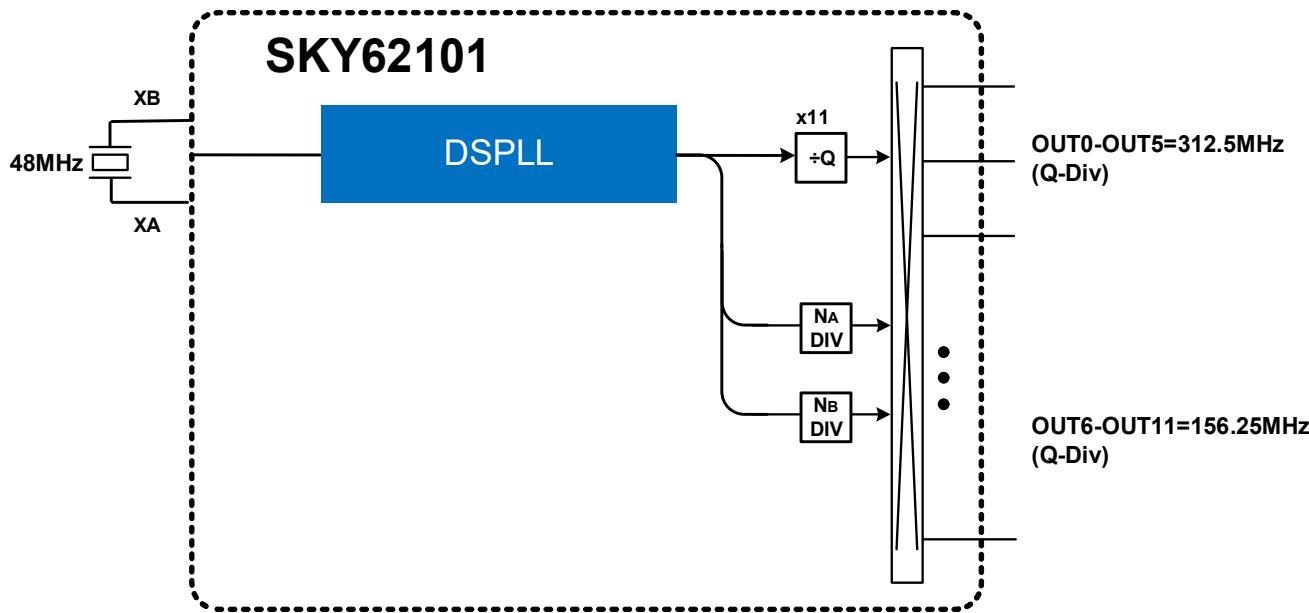

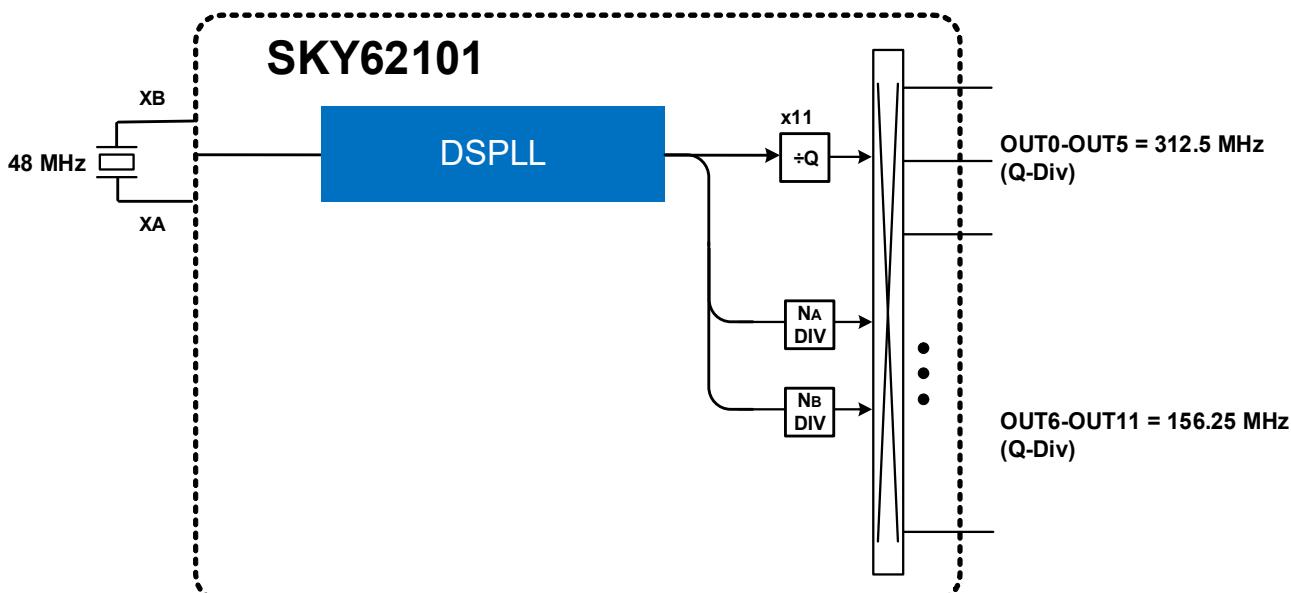

The SKY62101 clock generator combines Fifth-generation DSPLL® and MultiSynth™ technologies with an ultra-low jitter VCO to deliver ultra-low jitter (<55 fs) in PCIe Gen 1/2/3/4/5/6/7 compliant high-performance applications. The device is used in applications like 112G/224G SerDes, coherent optics, and data center equipment that demand the highest level of integration and jitter performance. All PLL components are integrated on-chip, eliminating the risk of noise coupling associated with discrete solutions.

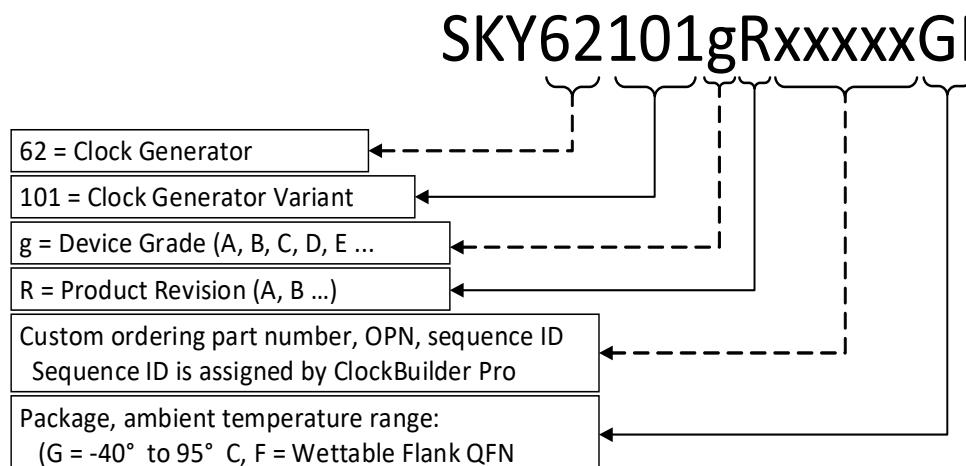

The SKY62101 supports free-run and synchronous operation by locking to an external crystal or oscillator. The SKY62101 is quickly and easily configured using Skyworks ClockBuilder® Pro (CBPro) software. ClockBuilder Pro assigns a custom part number for each unique configuration.

Devices ordered with custom part numbers are factory-programmed, making it easy to get a custom clock configuration uniquely tailored for each application. Custom part numbers that are factory-programmed will power up with a known frequency configuration. The device may also be user-configured at power-up or internally configured in non-volatile memory (NVM) using the CBPro Field Programmer via the serial interface. For more information, visit the [Skyworks Sales Information page](#).

### Applications

- 56G/112G/224G PAM4 serializer/deserializer (SerDes) clocking

- OTN muxponders and transponders

- 100/200/400/600/800G networking line cards

- Synchronous Ethernet

- Data center switches

- 100G/200G/400G optical transceivers

- Medical imaging

- Test and measurement

### Key Features

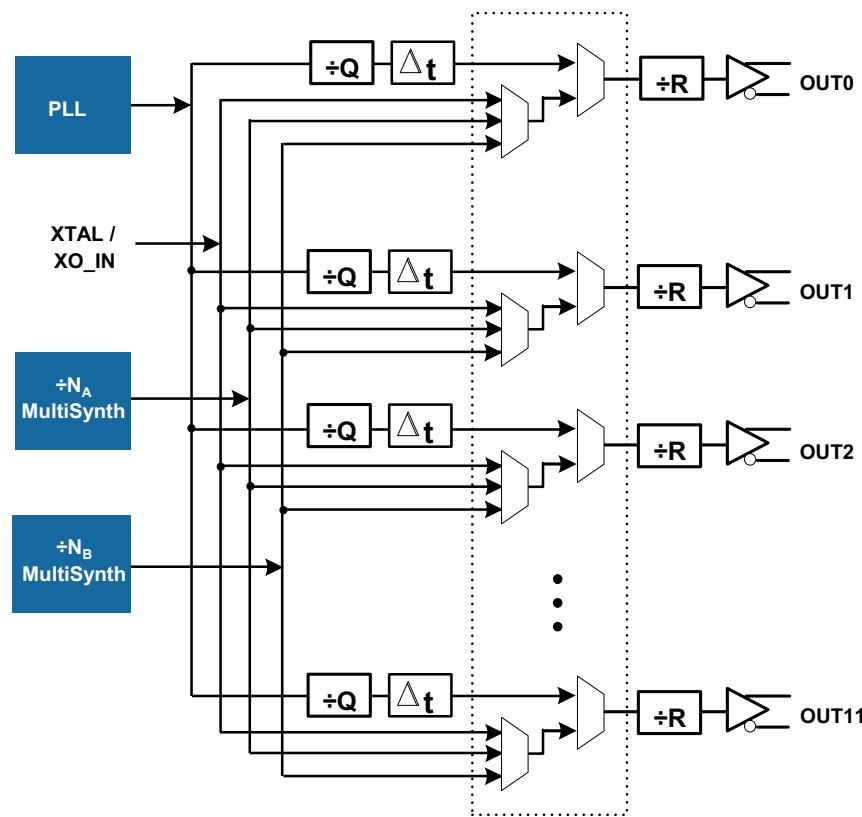

- Utilizes Fifth-generation DSPLL and MultiSynth technologies:

- One DSPLL, two MultiSynth

- Frequencies up to 3.2 GHz

- Ultra-low phase jitter:

- <55 fs RMS typ (integer mode)

- 100 fs RMS typ (fractional mode)

- PCIe Gen 1/2/3/4/5/6/7 compliant

- 12 outputs

- Output frequency range:

- Differential: 8 kHz to 3.2 GHz

- LVCMOS: 8 kHz to 250 MHz

- Fixed or user-adjustable output formats

- Programmable delay at each output

- External flash or internal NVM options

- Simplified API interface

- Pin-compatible with SKY63104/05/06 jitter attenuators and SKY63001/69003/69102 IEEE 1588 PTP network synchronizers

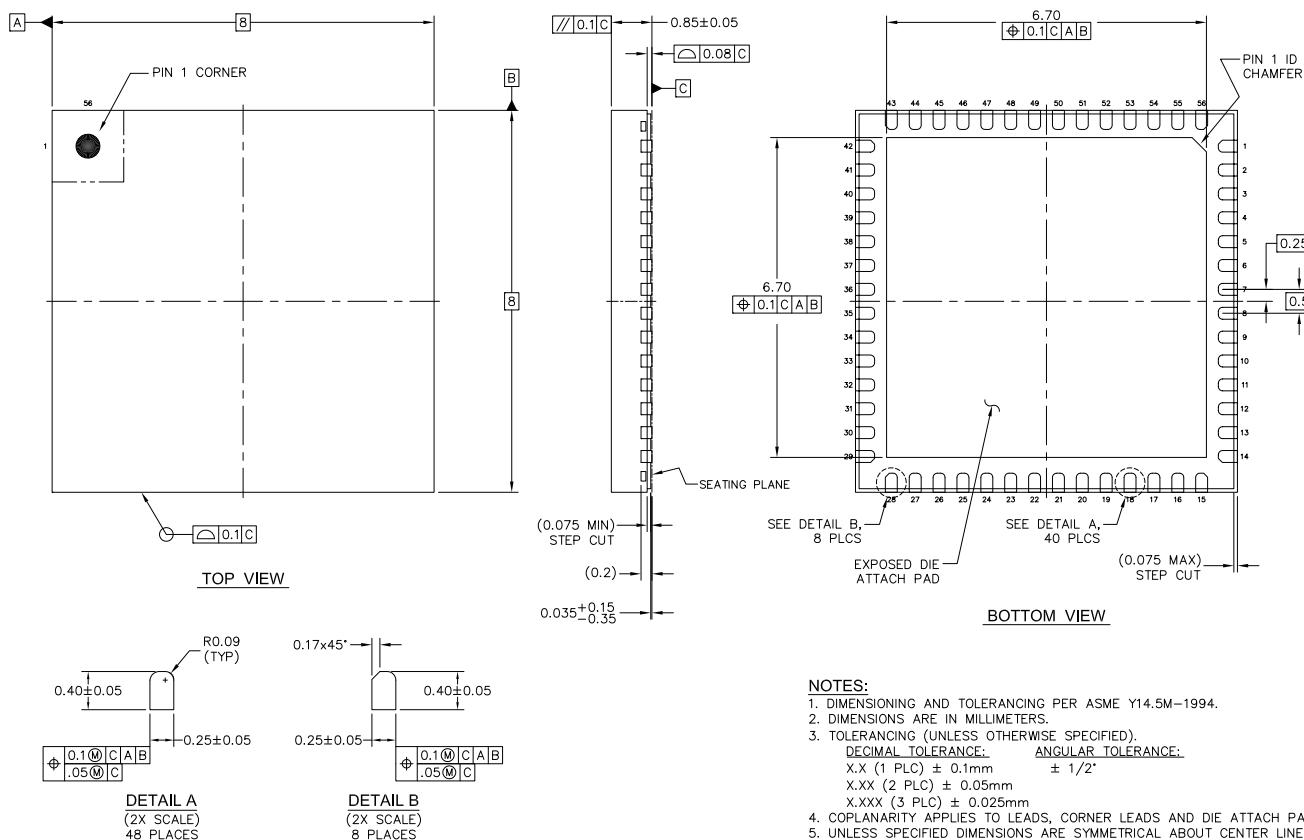

- 56-QFN, 8 x 8 mm

- ClockBuilder Pro Configuration Software

- For RoHS and other product compliance information, see the [Skyworks Certificate of Conformance](#).

## 1. Features List

Specifications on this page are for reference only. Refer to [3. "Electrical and Mechanical Specifications"](#) for device performance.

- Generates any output frequency in any format

- Ultra-low jitter performance

- <55 fs RMS typ. in integer mode

- 100 fs RMS typ. in fractional mode

- External crystal: 48 MHz to 61.44 MHz

- Up to 12 programmable clock outputs

- Integer divider

- Differential: 8 kHz to 3.2 GHz

- CMOS: 8 kHz to 250 MHz

- Fractional divider

- Differential: 8 kHz to 650 MHz

- CMOS: 8 kHz to 250 MHz

- Highly configurable outputs:

- Fixed formats LVDS, S-LVDS, LVPECL, LVCMS, CML, and HCSL

- User-programmable signal amplitude

- Configurable GPIO pins

- PCIe Gen 1/2/3/4/5/6/7 compliant

- PCIe spread spectrum support

- Programmable down and center spread spectrum

- Glitchless on-the-fly output frequency changes

- DCO Mode: as low as 0.001 ppb steps

- Core voltage: 3.3 V, 1.8 V

- Output supply pins: 3.3 V, 2.5 V, 1.8 V

- Serial Interface: I<sup>2</sup>C or SPI (3- or 4-wire)

- ClockBuilder Pro software tool simplifies device configuration

- External Flash support

- Package: 56-lead QFN, 8x8 mm

- Extended temperature range

- -40 to +95 °C ambient

- -40 to +105 °C board

- Pb-free, RoHS compliant

## 2. Pin Descriptions

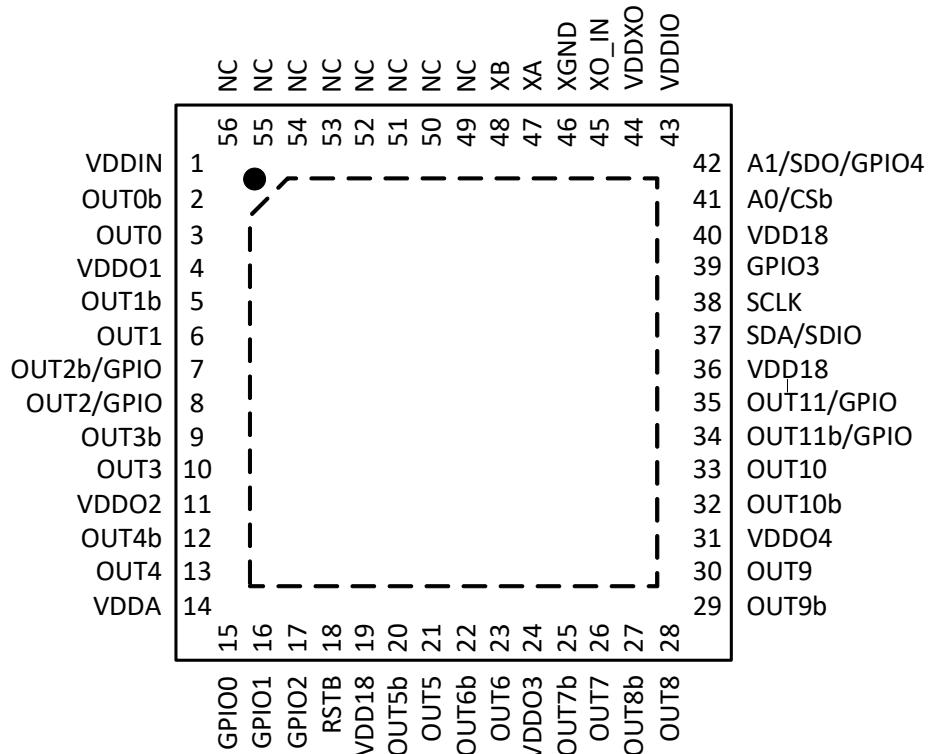

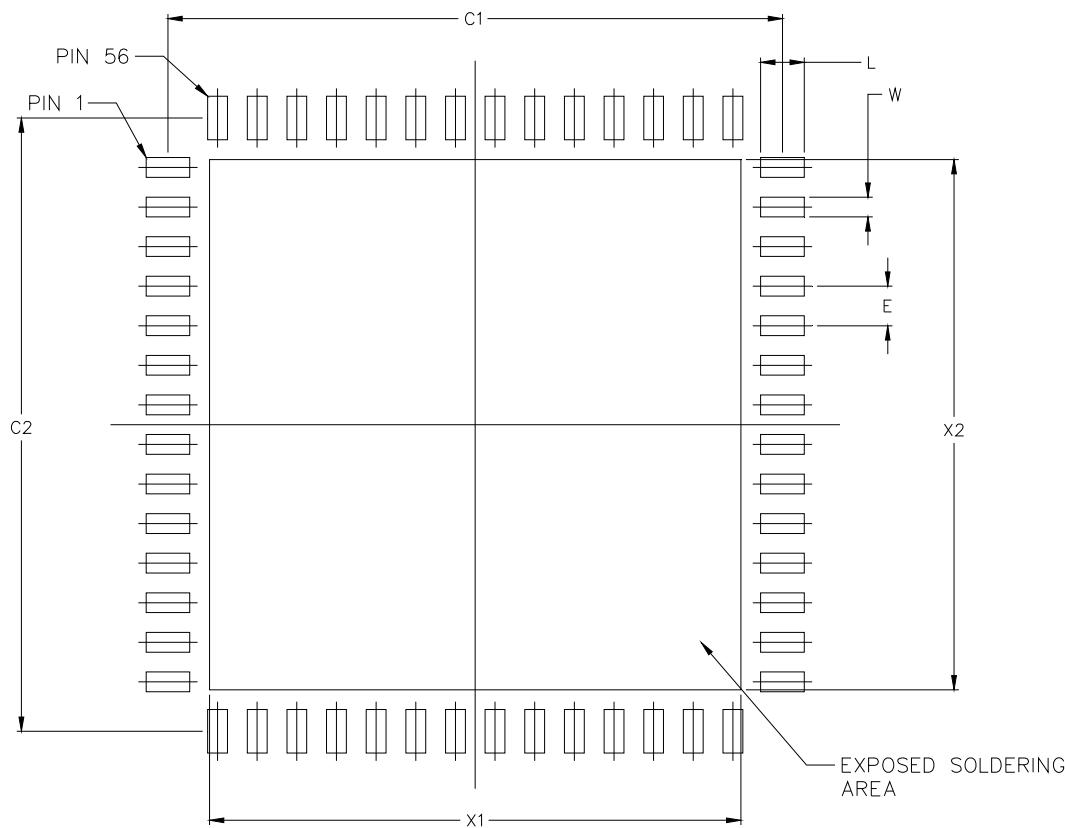

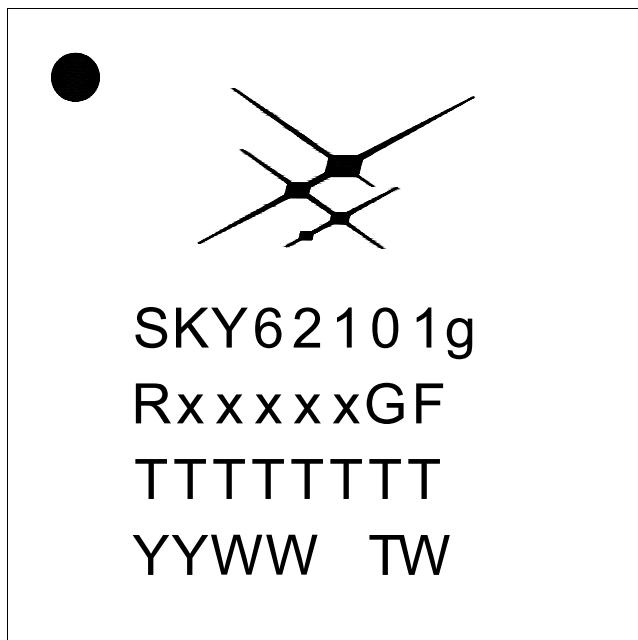

**Figure 2. Pinout Top View**

**Table 1.** Pin Descriptions

| Pin Name      | Pin Number | Pin Type <sup>1</sup> | Function                                                                                                                                                                                                                                                                        |

|---------------|------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Inputs</b> |            |                       |                                                                                                                                                                                                                                                                                 |

| XO_IN         | 45         | I                     | <b>Input for low phase noise (XO)</b>                                                                                                                                                                                                                                           |

| XGND          | 46         | I                     | <b>XTAL Shield</b><br>Connect this pin directly to the XTAL and capacitor ground pins. Do not ground the XV pin. XV should be isolated from the PCB ground plane. Refer to the <a href="#">"Fifth Generation DSPLL Clock Generator Reference Manual"</a> for layout guidelines. |

| XA            | 47         | I                     | <b>Crystal Input</b><br>Input pins for external crystal (XTAL). XA and XB pins can be left unconnected when not in use.                                                                                                                                                         |

| XB            | 48         |                       |                                                                                                                                                                                                                                                                                 |

Table 1. Pin Descriptions (Continued)

| Pin Name       | Pin Number | Pin Type <sup>1</sup> | Function                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------|------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NC             | 49         | NC                    | <b>No Connect</b><br>Leave these pins floating.                                                                                                                                                                                                                                                                                                                                                                                                      |

| NC             | 50         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| NC             | 51         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| NC             | 52         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| NC             | 53         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| NC             | 54         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| NC             | 55         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| NC             | 56         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <b>Outputs</b> |            |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

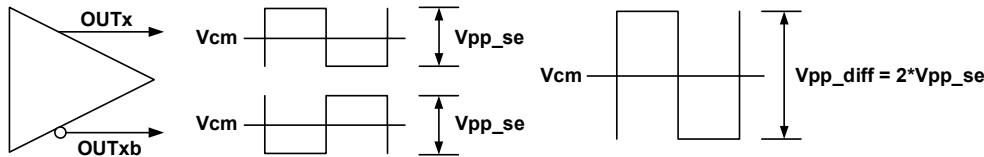

| OUT0b          | 2          | O                     | <b>Output Clocks</b><br>The output clocks can be programmed as single-ended CMOS or differential LVDS, S-LVDS, CML, HCSL or ac-coupled LVPECL and support a programmable signal amplitude and common-mode voltage. Desired output signal format is configurable in CBPro. Termination recommendations are provided in the <a href="#">"Fifth Generation DSPLL Clock Generator Reference Manual"</a> . Unused outputs should be left unconnected.     |

| OUT0           | 3          |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT1b          | 5          |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT1           | 6          |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT2b/GPIO     | 7          | I or O                | <b>Output Clocks with General-Purpose Input or Output Option</b><br>Output 2 can alternatively be assigned as two General-Purpose Inputs or Outputs (GPIO0, GPIO1) that can be programmed to have any of the input or output control functions listed in <a href="#">"5.6. GPIO Pins General Purpose Input or Output" on page 29</a> . Regardless of whether Output 2 is functioning as a clock output or GPIO, the power supply will be VDDO1.      |

| OUT2/GPIO      | 8          |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT3b          | 9          | O                     | <b>Output Clocks</b><br>The output clocks can be programmed as single-ended CMOS or differential LVDS, S-LVDS, CML, HCSL or ac-coupled LVPECL and support a programmable signal amplitude and common-mode voltage. The desired output signal format is configurable in CBPro. Termination recommendations are provided in the <a href="#">"Fifth Generation DSPLL Clock Generator Reference Manual"</a> . Unused outputs should be left unconnected. |

| OUT3           | 10         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT4b          | 12         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT4           | 13         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT5b          | 20         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT5           | 21         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT6b          | 22         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT6           | 23         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT7b          | 25         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT7           | 26         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT8b          | 27         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT8           | 28         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT9b          | 29         | I or O                | <b>Output Clocks with General-Purpose Input or Output Option</b><br>Output 11 can alternatively be assigned as two General Purpose Inputs or Outputs (GPIO2, GPIO3) that can be programmed to have any of the input or output control functions listed in <a href="#">"5.6. GPIO Pins General Purpose Input or Output" on page 29</a> . Regardless of whether Output 11 is functioning as a clock output or GPIO, the power supply will be VDDO4.    |

| OUT9           | 30         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT10b         | 32         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT10          | 33         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT11b/GPIO    | 34         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT11/GPIO     | 35         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Table 1. Pin Descriptions (Continued)

| Pin Name                | Pin Number | Pin Type <sup>1</sup> | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------|------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Serial Interface</b> |            |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SDA/SDIO                | 37         | I/O                   | <b>Serial Data Interface</b><br>This is the bidirectional data pin (SDA) for the I <sup>2</sup> C mode, or the bidirectional data pin (SDIO) in the 3-wire SPI mode, or the input data pin (SDI) in the 4-wire SPI mode. When in I <sup>2</sup> C mode, this pin must be pulled-up using an external resistor of at least 1 kΩ. No pull-up resistor is needed when in SPI mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SCLK                    | 38         | I                     | <b>Serial Clock Input Interface</b><br>This is the bidirectional I <sup>2</sup> C clock pin. Clock stretching (i.e., driving SCL low to insert wait-states) will be utilized when operating at rates greater than 100 kHz. This pin must be pulled up to V <sub>DDIO</sub> using an external resistor of at least 1 kΩ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| A0/CSb                  | 41         | I                     | <b>Address Select 0/Chip Select</b><br>This pin functions as the hardware-controlled LSB of the device address (A0) in I <sup>2</sup> C mode. In SPI mode, this pin functions as the chip select input (active low). This pin is internally pulled up and can be left floating if unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| A1/SDO/GPIO4            | 42         | O                     | <b>Address Select 1/Serial Data Output/GPIO4</b><br>This input pin operates as the hardware-controlled next to LSB portion of the device address (A1) in I <sup>2</sup> C mode. In 4-wire SPI mode, this pin operates as the Serial Data Output (SDO). In 3-wire SPI mode, this pin can function as an additional GPIO pin (GPIO4).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <b>Control/Status</b>   |            |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GPIO0                   | 15         | I or O                | <b>Programmable General Purpose Input or Outputs</b><br>These pins can be programmed to the functions defined in "5.6. GPIO Pins General Purpose Input or Output" on page 29. See the "Fifth Generation DSPLL Clock Generator Reference Manual" for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| GPIO1                   | 16         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GPIO2                   | 17         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GPIO3                   | 39         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

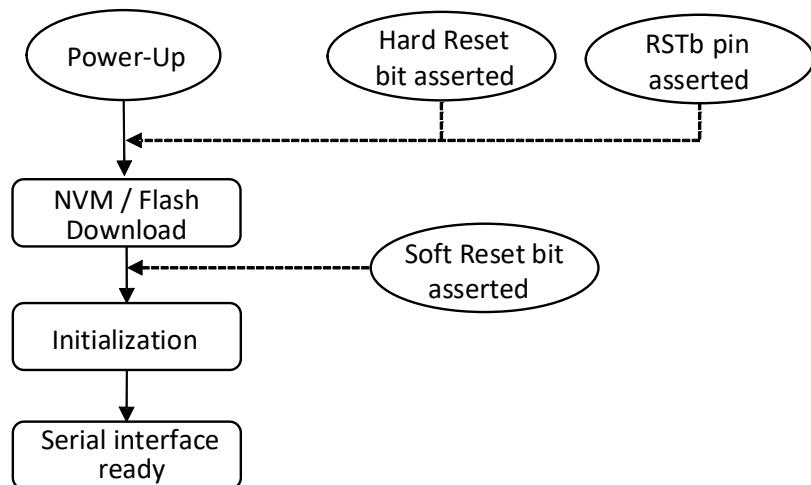

| RSTb                    | 18         | I                     | <b>Device Reset</b><br>This pin functions as an active-low reset input and is used to generate a device reset when held low for at least the specified minimum pulse width. This resets the device back to a known state and reloads the NVM frequency plan and application. All clocks will stop while the RSTb pin is asserted. If there is no frequency plan in NVM, the reset pin will return the device to the bootloader state in which it is waiting for the frequency plan and application to be downloaded by the host controller. This pin accepts a CMOS input and is internally pulled up with a ~20 kΩ resistor to V <sub>DDIO</sub> . VDDA and VDD18 must be powered up and stable before releasing RSTb. RSTb must not be toggled faster than the maximum update rate (f <sub>UR</sub> ) specification. For more details on RSTb pin circuitry, refer to the "Fifth Generation DSPLL Clock Generator Reference Manual". |

| <b>Power</b>            |            |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VDDIN                   | 1          | P                     | <b>Input Clock Supply Voltage</b><br>Supply voltage 3.3 V, 2.5 V or 1.8 V for the input clock buffers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VDDO1                   | 4          | P                     | <b>Output Clock Supply VDDO1 to VDDO4</b><br>Supply voltage 3.3 V, 2.5 V, or 1.8 V for outputs. Leave VDDO pins of unused output drivers unconnected. An alternate option is to connect the VDDO pin to a power supply and disable the output driver to minimize current consumption. A 0402 1 μF capacitor should be placed very near each of these pins. VDDO may not exceed VDDA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VDDO2                   | 11         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VDDO3                   | 24         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VDDO4                   | 31         |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Table 1. Pin Descriptions (Continued)

| Pin Name | Pin Number     | Pin Type <sup>1</sup> | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|----------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDDA     | 14             | P                     | <b>Core Analog Supply Voltage</b><br>This core supply can operate from a 3.3 V or 1.8 V power supply for low-power mode. Note that all other supply voltages must be equal or lower voltage than the VDDA pin, so in low-power mode, no other supply can exceed 1.8 V. See the <a href="#">"Fifth Generation DSPLL Clock Generator Reference Manual"</a> for power supply filtering recommendations. A 0402 1 $\mu$ F capacitor should be placed very near each of these pins. |

| VDD18    | 19             | P                     | <b>Core Supply Voltage 1.8 V</b>                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VDD18    | 36             |                       | The device core operates from a 1.8 V supply. See the <a href="#">"Fifth Generation DSPLL Clock Generator Reference Manual"</a> for power supply filtering recommendations. A 0402 1 $\mu$ F capacitor should be placed very near each of these pins.                                                                                                                                                                                                                          |

| VDD18    | 40             |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| VDDIO    | 43             | P                     | <b>Control, Status IO Clock Supply Voltage</b><br>Supply voltage 3.3 V, 2.5 V, or 1.8 V for the serial interface, control, and status inputs and outputs.                                                                                                                                                                                                                                                                                                                      |

| VDDXO    | 44             | P                     | <b>Reference Supply Voltage</b><br>Supply voltage of 3.3 V or 1.8 V supported for the reference. For best performance, VDDXO should be the same voltage as the VDD_XO.                                                                                                                                                                                                                                                                                                         |

| GND PAD  | Package Bottom | P                     | <b>Exposed Die Attach Pad</b><br>The exposed die attach pad (ePAD) on the bottom of the package must be connected to electrical ground.                                                                                                                                                                                                                                                                                                                                        |

1. I = Input, O = Output, P = Power, NC = No Connect.

### 3. Electrical and Mechanical Specifications

All minimum and maximum specifications are assured and apply across the recommended operating conditions. Typical values apply at nominal supply voltages and an operating temperature of 25 °C unless otherwise noted.

**Table 2. Absolute Maximum Ratings<sup>1,2,3</sup>**

| Parameter                                                   | Symbol     | Test Condition                        | Value            | Unit |

|-------------------------------------------------------------|------------|---------------------------------------|------------------|------|

| DC supply voltage                                           | $V_{DDIN}$ |                                       | −0.5 to 3.8      | V    |

|                                                             | $V_{DDXO}$ |                                       | −0.5 to 3.8      | V    |

|                                                             | $V_{DD18}$ | <10 s                                 | −0.5 to 2.4      | V    |

|                                                             | $V_{DDA}$  | <10 s                                 | −0.5 to 3.8      | V    |

|                                                             | $V_{DDO}$  | <10 s                                 | −0.5 to 3.8      | V    |

|                                                             | $V_{DDIO}$ | <10 s                                 | −0.5 to 3.8      | V    |

| Input voltage range                                         | $V_{I1}$   | XO_IN/XO_INb                          | −0.85 to 3.8     | V    |

|                                                             | $V_{I2}$   | GPIO0-3, RSTb, SCLK, SDA/SDIO, A0/CSb | −0.5 to 3.8      | V    |

|                                                             | $V_{I3}$   | XA/XB                                 | −0.5 to 2.7      | V    |

| Latch-up tolerance                                          | LU         |                                       | JESD78 compliant |      |

| ESD tolerance                                               | HBM        | 100 pF, 1.5 kΩ                        | 2.0              | kV   |

| Storage range                                               | TSTG       |                                       | −55 to 150       | °C   |

| Maximum junction temperature in operation                   | $T_{JCT}$  |                                       | 125              | °C   |

| Soldering temperature (Pb-free profile) <sup>4</sup>        | $T_{PEAK}$ |                                       | 235 to 245       | °C   |

| Soldering time at $T_{PEAK}$ (Pb-free profile) <sup>4</sup> | $T_p$      |                                       | 30 to 40         | s    |

1. Permanent device damage may occur if the absolute maximum ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

2. RoHS-6 compliant.

3. For more packaging information, visit the [Skyworks environmental compliance page](#).

4. The device is compliant with JEDEC J-STD-020.

*ESD Handling: Industry-standard ESD handling precautions must be adhered to at all times to avoid damage to this device.*

Table 3. Thermal Conditions

| Parameter                                  | Symbol                   | Test Condition | Typical Value      |                   | Unit |

|--------------------------------------------|--------------------------|----------------|--------------------|-------------------|------|

|                                            |                          |                | JEDEC <sup>1</sup> | CEVB <sup>2</sup> |      |

| Thermal resistance, junction-to-ambient    | $\theta_{JA}$            | Still air      | 23.27              | 9.89              | °C/W |

|                                            |                          | 1 m/s          | 19.44              | 8.60              | °C/W |

|                                            |                          | 2 m/s          | 18.65              | 8.52              | °C/W |

| Thermal resistance, junction-to-board      | $\Psi_{JB}$ <sup>3</sup> | Still air      | 10.21              | 3.85              | °C/W |

| Thermal resistance, junction-to-top-center | $\Psi_{JC}$              | Still air      | 0.4                | 0.6               | °C/W |

1. Based on PCB dimension: 4" x 4.5", PCB thickness: 1.6 mm, number of Cu Layers: 2.

2. Customer EVB: eight-layer board, board dimensions: ~9" x 9", all eight layers are copper-poured.

3.  $\Psi_{JB}$  can be used to calculate the junction temperature based on the board temperature and power dissipation for a given frequency plan,  $T_j = T_{PCB} + \Psi_{JB} \times P_D$ .  $T_{PCB}$  should be measured as close to the SKY62101 DUT as possible since temperature may vary across the PCB.

Table 4. Recommended Operating Conditions

$V_{DD18} = 1.8 \text{ V} \pm 5\%$ ,  $V_{DDXO} = V_{DDA} = 3.3 \text{ V} \pm 5\%$ , All other supplies programmable  $3.3 \text{ V} \pm 5\%$ ,  $2.5 \text{ V} \pm 5\%$ ,  $1.8 \text{ V} \pm 5\%$ ,  $T_A = -40$  to  $95 \text{ }^\circ\text{C}$ .

Low Power Mode:  $V_{DD18} = V_{DDIN} = V_{DDIO} = V_{DDXO} = V_{DDA} = V_{DDO} = 1.8 \text{ V} \pm 5\%$ ,  $T_A = -40$  to  $95 \text{ }^\circ\text{C}$ .

| Parameter                          | Symbol                  | Test Condition | Min  | Typ  | Max                    | Unit |

|------------------------------------|-------------------------|----------------|------|------|------------------------|------|

| Ambient temperature                | $T_A$                   |                | -40  | 25   | 95                     | °C   |

| Board temperature                  | $T_B$                   |                | -40  | 65   | 105                    | °C   |

| Junction temperature               | $T_{JMAX}$ <sup>1</sup> |                | —    | —    | 125                    | °C   |

| Core supply voltage                | $V_{DD18}$              |                | 1.71 | 1.80 | 1.89                   | V    |

|                                    | $V_{DDA}$ <sup>2</sup>  |                | 3.14 | 3.30 | 3.47                   | V    |

|                                    |                         | Low-power mode | 1.71 | 1.80 | 1.89                   | V    |

|                                    | $V_{DDXO}$              |                | 3.14 | 3.30 | $V_{DDA}$ <sup>2</sup> | V    |

|                                    |                         | Low-power mode | 1.71 | 1.80 | 1.89                   | V    |

| Input supply voltage               | $V_{DDIN}$              |                | 3.14 | 3.30 | $V_{DDA}$ <sup>2</sup> | V    |

|                                    |                         |                | 2.38 | 2.50 | 2.62                   | V    |

|                                    |                         |                | 1.71 | 1.80 | 1.89                   | V    |

| GPIO supply voltage                | $V_{DDIO}$              |                | 3.14 | 3.30 | $V_{DDA}$ <sup>2</sup> | V    |

|                                    |                         |                | 2.38 | 2.50 | 2.62                   | V    |

|                                    |                         |                | 1.71 | 1.80 | 1.89                   | V    |

| Clock output driver supply voltage | $V_{DDO}$               |                | 3.14 | 3.30 | $V_{DDA}$ <sup>2</sup> | V    |

|                                    |                         |                | 2.38 | 2.50 | 2.62                   | V    |

|                                    |                         |                | 1.71 | 1.80 | 1.89                   | V    |

1. Ambient temperature of  $95 \text{ }^\circ\text{C}$  may not be possible with all configurations. This is dependent on device configuration.  $T_j$  cannot exceed a max of  $125 \text{ }^\circ\text{C}$ .

2.  $VDDA$  must be greater than or equal to the highest voltage applied to the device. In Low-Power Mode, all voltage supplies must be set to  $1.8 \text{ V}$ .

**Table 5. Performance Characteristics**

$V_{DD18} = 1.8 \text{ V} \pm 5\%$ ,  $V_{DDA} = V_{DDXO} = 3.3 \text{ V} \pm 5\%$ ; All other supplies programmable  $3.3 \text{ V} \pm 5\%$ ,  $2.5 \text{ V} \pm 5\%$ ,  $1.8 \text{ V} \pm 5\%$ ,  $T_A = -40 \text{ to } 95 \text{ }^\circ\text{C}$ .

Low-Power Mode:  $V_{DD18} = V_{DDIN} = V_{DDIO} = V_{DDXO} = V_{DDA} = V_{DDO} = 1.8 \text{ V} \pm 5\%$ ,  $T_A = -40 \text{ to } 95 \text{ }^\circ\text{C}$ .

| Parameter                                                              | Symbol                  | Comment                                                                           | Min                          | Typ                | Max                          | Unit |

|------------------------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------|------------------------------|--------------------|------------------------------|------|

| Initial start-up time                                                  | $t_{\text{START}}^1$    | Time from POR to when the device generates output clocks from NVM frequency plan. | —                            | 25                 | 40                           | ms   |

|                                                                        | $t_{\text{RDY}}$        | POR to API ready                                                                  | —                            | 25                 | 30                           | ms   |

| Output delay adjustment<br>(typical $T_{\text{VCO}} = 90 \text{ ps}$ ) | $t_{\text{QDIV}}$       | Range <sup>2</sup>                                                                | $-T_{\text{VCO}} \times 127$ | —                  | $+T_{\text{VCO}} \times 127$ | ps   |

|                                                                        |                         | Resolution                                                                        |                              | $T_{\text{VCO}}$   | —                            | ps   |

|                                                                        |                         | Resolution (fine delay enabled)                                                   |                              | $T_{\text{VCO}}/4$ | —                            | ps   |

| Pull-in range                                                          | $\omega_p$              |                                                                                   | —                            | $\pm 100$          | —                            | ppm  |

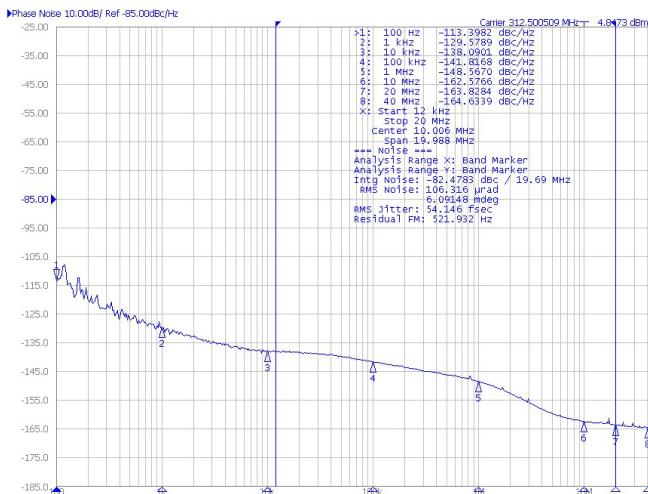

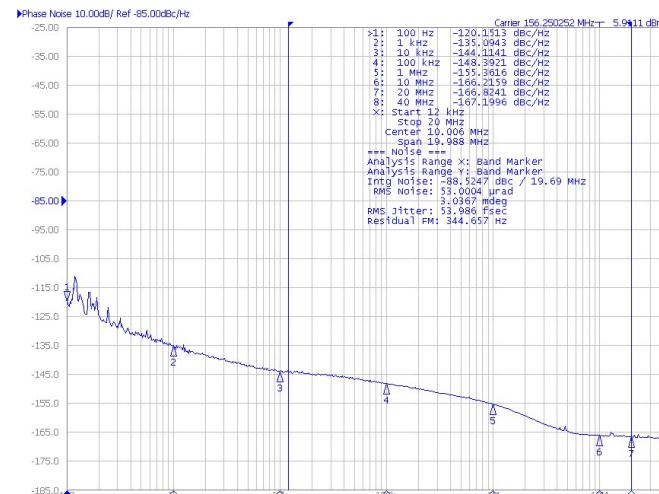

| RMS jitter crystal reference <sup>3,4</sup>                            | Q Div                   | 644.53125 MHz                                                                     | —                            | 52                 | 70                           | fs   |

|                                                                        |                         | 625 MHz                                                                           | —                            | 53                 | 82                           | fs   |

|                                                                        |                         | 390.625 MHz                                                                       | —                            | 52                 | 70                           | fs   |

|                                                                        |                         | 322.265625 MHz                                                                    | —                            | 52                 | 70                           | fs   |

|                                                                        |                         | 312.5 MHz                                                                         | —                            | 54                 | 70                           | fs   |

|                                                                        |                         | 156.25 MHz                                                                        |                              | 55                 | 74                           | fs   |

|                                                                        |                         | 125 MHz                                                                           |                              | 60                 | 80                           | fs   |

|                                                                        | MultiSynth<br>NA/NB Div | 100 MHz                                                                           |                              | 65                 | 85                           | fs   |

|                                                                        |                         | 644.53125 MHz                                                                     | —                            | 57                 | 75                           | fs   |

|                                                                        |                         | 322.265625 MHz                                                                    | —                            | 58                 | 80                           | fs   |

|                                                                        |                         | 156.25 MHz                                                                        | —                            | 64                 | 85                           | fs   |

|                                                                        |                         | 125 MHz                                                                           | —                            | 70                 | 96                           | fs   |

|                                                                        |                         | 100 MHz                                                                           | —                            | 112                | 130                          | fs   |

|                                                                        |                         |                                                                                   |                              |                    |                              |      |

| Buffered output jitter performance,<br>12 kHz to 20 MHz.               |                         | Crystal mode                                                                      | —                            | 78                 | —                            | fs   |

|                                                                        |                         | XO_IN additive jitter                                                             | —                            | 39                 | —                            | fs   |

- Assumes crystal or XO is available at power up.

- Output delay adjustment range will vary depending on frequency plan. Output delay adjustment range (ns) is displayed in the “Output Skew Control” step of the CBPro Wizard.  $f_{\text{VCO}}$  range is 10.4 to 13.0 GHz.

- Added jitter and spurs due to crosstalk is frequency plan dependent and can be determined using the ClockBuilder Pro Spur Analysis tool.

- Jitter generation test conditions: XTAL = 54 MHz TXC 7M54070001,  $f_{\text{VCO}} < 11 \text{ GHz}$ ;  $f_{\text{OUT}}$  LVDS, DSPLL BW = 40 Hz.

**Table 6. 100 MHz PCIe Jitter Performance Characteristics (without Spread Spectrum)**

$V_{DD18} = 1.8 \text{ V} \pm 5\%$ ,  $V_{DDA} = V_{DDXO} = 3.3 \text{ V} \pm 5\%$ ; All other supplies programmable  $3.3 \text{ V} \pm 5\%$ ,  $2.5 \text{ V} \pm 5\%$ ,  $1.8 \text{ V} \pm 5\%$ ,  $T_A = -40 \text{ to } 95 \text{ }^\circ\text{C}$ .

Low-Power Mode:  $V_{DD18} = V_{DDIN} = V_{DDIO} = V_{DDXO} = V_{DDA} = V_{DDO} = 1.8 \text{ V} \pm 5\%$ ,  $T_A = -40 \text{ to } 95 \text{ }^\circ\text{C}$ .

| Parameter                                                             | Symbol            | Comment                    | Min | Typ | Max | PCI-SIG Limit <sup>1</sup> | Unit              |

|-----------------------------------------------------------------------|-------------------|----------------------------|-----|-----|-----|----------------------------|-------------------|

| 100 MHz PCIe common clock jitter performance <sup>2</sup>             | DSPLL + Qdiv      | Gen 1 (2.5GT/s)            | —   | 14  | 56  | 86                         | ps <sub>p-p</sub> |

|                                                                       |                   | Gen 2 (5GT/s)<br>Low Band  | —   | 2   | 29  | 3000                       | fs <sub>RMS</sub> |

|                                                                       |                   | Gen 2 (5GT/s)<br>High Band | —   | 86  | 860 | 3100                       | fs <sub>RMS</sub> |

|                                                                       |                   | Gen 3 (8GT/s)              | —   | 24  | 172 | 1000                       | fs <sub>RMS</sub> |

|                                                                       |                   | Gen 4 (16GT/s)             | —   | 23  | 172 | 500                        | fs <sub>RMS</sub> |

|                                                                       |                   | Gen 5 (32GT/s)             | —   | 6   | 46  | 150                        | fs <sub>RMS</sub> |

|                                                                       |                   | Gen 6 (64GT/s)             | —   | 6   | 40  | 100                        | fs <sub>RMS</sub> |

|                                                                       |                   | Gen 7 (128GT/s)            | —   | 4   | 28  | 67                         | fs <sub>RMS</sub> |

|                                                                       | DSPLL + NA/NB Div | Gen 1 (2.5GT/s)            | —   | 14  | 57  | 86                         | ps <sub>p-p</sub> |

|                                                                       |                   | Gen 2 (5GT/s)<br>Low Band  | —   | 2   | 30  | 3000                       | fs <sub>RMS</sub> |

|                                                                       |                   | Gen 2 (5GT/s)<br>High Band | —   | 117 | 901 | 3100                       | fs <sub>RMS</sub> |

|                                                                       |                   | Gen 3 (8GT/s)              | —   | 34  | 182 | 1000                       | fs <sub>RMS</sub> |

|                                                                       |                   | Gen 4 (16GT/s)             | —   | 33  | 182 | 500                        | fs <sub>RMS</sub> |

|                                                                       |                   | Gen 5 (32GT/s)             | —   | 12  | 49  | 150                        | fs <sub>RMS</sub> |

|                                                                       |                   | Gen 6 (64GT/s)             | —   | 8   | 42  | 100                        | fs <sub>RMS</sub> |

|                                                                       |                   | Gen 7 (128GT/s)            | —   | 6   | 29  | 67                         | fs <sub>RMS</sub> |

| 100 MHz PCIe separate reference clock jitter performance <sup>2</sup> | DSPLL + Qdiv      | Gen 2 (5GT/s)<br>Low Band  | —   | 3   | 5   | 2120                       | fs <sub>RMS</sub> |

|                                                                       |                   | Gen 2 (5GT/s)<br>High Band | —   | 117 | 646 | 2190                       | fs <sub>RMS</sub> |

|                                                                       |                   | Gen 3 (8GT/s)              | —   | 30  | 129 | 707                        | fs <sub>RMS</sub> |

|                                                                       |                   | Gen 4 (16GT/s)             | —   | 30  | 129 | 495                        | fs <sub>RMS</sub> |

|                                                                       |                   | Gen 5 (32GT/s)             | —   | 11  | 54  | 177                        | fs <sub>RMS</sub> |

|                                                                       |                   | Gen 6 (64GT/s)             | —   | 10  | 54  | 106                        | fs <sub>RMS</sub> |

|                                                                       |                   | Gen 7 (128GT/s)            | —   | 7   | 38  | 71                         | fs <sub>RMS</sub> |

|                                                                       | DSPLL + NA/NB Div | Gen 2 (5GT/s)<br>Low Band  | —   | 3   | 5   | 2120                       | fs <sub>RMS</sub> |

|                                                                       |                   | Gen 2 (5GT/s)<br>High Band | —   | 142 | 679 | 2190                       | fs <sub>RMS</sub> |

|                                                                       |                   | Gen 3 (8GT/s)              | —   | 37  | 137 | 707                        | fs <sub>RMS</sub> |

|                                                                       |                   | Gen 4 (16GT/s)             | —   | 37  | 137 | 495                        | fs <sub>RMS</sub> |

|                                                                       |                   | Gen 5 (32GT/s)             | —   | 15  | 57  | 177                        | fs <sub>RMS</sub> |

|                                                                       |                   | Gen 6 (64GT/s)             | —   | 12  | 57  | 106                        | fs <sub>RMS</sub> |

|                                                                       |                   | Gen 7 (128GT/s)            | —   | 9   | 40  | 71                         | fs <sub>RMS</sub> |

1. PCI-SIG does not specify a jitter limit for separate reference clock architectures. Instead the PCI-SIG specified simulation limit can be split evenly between transmitter and receiver clocks by dividing by the square root of 2 since their jitter is uncorrelated.

2. Jitter integration as specified by PCI-SIG in the PCI Express® Base Specification Revision 7.0.

**Table 7. 100 MHz PCIe Jitter Performance Characteristics (with Spread Spectrum)**

$V_{DD18} = 1.8 \text{ V} \pm 5\%$ ,  $V_{DDA} = V_{DDXO} = 3.3 \text{ V} \pm 5\%$ ; All other supplies programmable  $3.3 \text{ V} \pm 5\%$ ,  $2.5 \text{ V} \pm 5\%$ ,  $1.8 \text{ V} \pm 5\%$ ,  $T_A = -40 \text{ to } 95 \text{ }^\circ\text{C}$ .

Low-Power Mode:  $V_{DD18} = V_{DDIN} = V_{DDIO} = V_{DDXO} = V_{DDA} = V_{DDO} = 1.8 \text{ V} \pm 5\%$ ,  $T_A = -40 \text{ to } 95 \text{ }^\circ\text{C}$ .

| Parameter                                                               | Symbol         | Comment                    | Min | Typ | Max  | PCI-SIG Limit <sup>1</sup> | Unit                        |

|-------------------------------------------------------------------------|----------------|----------------------------|-----|-----|------|----------------------------|-----------------------------|

| 100 MHz PCIe common clock jitter performance <sup>2,3</sup>             | DSPLL + NB Div | Gen 1 (2.5GT/s)            | —   | 26  | 70   | 86                         | ps P-P                      |

|                                                                         |                | Gen 2 (5GT/s)<br>Low Band  | —   | 5   | 43   | 3000                       | $f_{\text{S}}_{\text{RMS}}$ |

|                                                                         |                | Gen 2 (5GT/s)<br>High Band | —   | 684 | 1880 | 3100                       | $f_{\text{S}}_{\text{RMS}}$ |

|                                                                         |                | Gen 3 (8GT/s)              | —   | 272 | 459  | 1000                       | $f_{\text{S}}_{\text{RMS}}$ |

|                                                                         |                | Gen 4 (16GT/s)             | —   | 191 | 326  | 500                        | $f_{\text{S}}_{\text{RMS}}$ |

|                                                                         |                | Gen 5 (32GT/s)             | —   | 55  | 103  | 150                        | $f_{\text{S}}_{\text{RMS}}$ |

|                                                                         |                | Gen 6 (64GT/s)             | —   | 37  | 72   | 100                        | $f_{\text{S}}_{\text{RMS}}$ |

|                                                                         |                | Gen 7 (128GT/s)            | —   | 26  | 51   | 67                         | $f_{\text{S}}_{\text{RMS}}$ |

| 100 MHz PCIe separate reference clock jitter performance <sup>2,4</sup> | DSPLL + NB Div | Gen 2 (5GT/s)<br>High Band | —   | 838 | 1047 | 2190                       | $f_{\text{S}}_{\text{RMS}}$ |

|                                                                         |                | Gen 3 (8GT/s)              | —   | 619 | 656  | 707                        | $f_{\text{S}}_{\text{RMS}}$ |

|                                                                         |                | Gen 4 (16GT/s)             | —   | 394 | 463  | 495                        | $f_{\text{S}}_{\text{RMS}}$ |

|                                                                         |                | Gen 5 (32GT/s)             | —   | 66  | 92   | 177                        | $f_{\text{S}}_{\text{RMS}}$ |

|                                                                         |                | Gen 6 (64GT/s)             | —   | 59  | 82   | 106                        | $f_{\text{S}}_{\text{RMS}}$ |

|                                                                         |                | Gen 7 (128GT/s)            | —   | 42  | 58   | 71                         | $f_{\text{S}}_{\text{RMS}}$ |

- PCI-SIG does not specify a jitter limit for separate reference clock architectures. Instead the PCI-SIG specified simulation limit can be split evenly between transmitter and receiver clocks by dividing by the square root of 2 since their jitter is uncorrelated.

- Jitter integration as specified by PCI-SIG in the PCI Express® Base Specification Revision 7.0.

- Common clock spread spectrum modulation of  $-0.4\%$ .

- Separate reference spread modulation of  $-0.4\%$  Gen2 to Gen4,  $-0.3\%$  Gen5 to Gen6, and  $-0.15\%$  Gen7.

**Table 8. DC Characteristics**

$V_{DD18} = 1.8 \text{ V} \pm 5\%$ ,  $V_{DDXO} = V_{DDA} = 3.3 \text{ V} \pm 5\%$ , All other supplies programmable  $3.3 \text{ V} \pm 5\%$ ,  $2.5 \text{ V} \pm 5\%$ ,  $1.8 \text{ V} \pm 5\%$ ,  $T_A = -40 \text{ to } 95 \text{ }^\circ\text{C}$ .

Low Power Mode:  $V_{DD18} = V_{DDIN} = V_{DDIO} = V_{DDXO} = V_{DDA} = V_{DDO} = 1.8 \text{ V} \pm 5\%$ ,  $T_A = -40 \text{ to } 95 \text{ }^\circ\text{C}$ .

| Parameter                                                      | Symbol                                       | Test Condition                                                            | Min | Typ | Max | Unit |

|----------------------------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------|-----|-----|-----|------|

| Core supply current ( $V_{DD12} + V_{DDA}$ )                   | $I_{DD18}$                                   | SKY62101 <sup>1,2</sup>                                                   | —   | 400 | 650 | mA   |

|                                                                | $I_{DDA}$                                    | SKY62101 <sup>1,2</sup>                                                   | —   | 190 | 230 | mA   |

|                                                                | $I_{DD18\_PD}$                               | $RSTb = 0$                                                                | —   | 120 | 300 | mA   |

|                                                                | $I_{DDA\_PD}$                                | $RSTb = 0$                                                                | —   | 15  | 16  | mA   |

| Peripheral supply current ( $V_{DDIN} + V_{DDIO} + V_{DDXO}$ ) | $I_{DDIN} + I_{DDIO}$                        | SKY62101 <sup>1,2</sup>                                                   | —   | 32  | 50  | mA   |

|                                                                | $I_{DDXO}$                                   | SKY62101 <sup>1,2</sup>                                                   | —   | 12  | 15  | mA   |

|                                                                | $I_{DDIN\_PD} + I_{DDIO\_PD} + I_{DDXO\_PD}$ | $RSTb = 0$                                                                | —   | 2   | 3   | mA   |

|                                                                |                                              |                                                                           |     |     |     |      |

| Output buffer supply current ( $V_{DDOX}$ )                    | $I_{DDOX}$<br>(per output)                   | LVPECL (2.5 V, 3.3 V) @ 156.25 MHz <sup>3</sup>                           | —   | 24  | 26  | mA   |

|                                                                |                                              | LVDS (2.5 V, 3.3 V) @ 156.25 MHz <sup>3</sup>                             | —   | 13  | 15  | mA   |

|                                                                |                                              | S-LVDS (1.8 V) @ 156.25 MHz <sup>3</sup>                                  | —   | 12  | 14  | mA   |

|                                                                |                                              | CML (1.8 V, 2.5 V, 3.3 V) @ 156.25 MHz <sup>3</sup>                       | —   | 14  | 17  | mA   |

|                                                                |                                              | 3.3 V LVCMOS @ 156.25 MHz <sup>4</sup>                                    | —   | 19  | 22  | mA   |

|                                                                |                                              | 2.5 V LVCMOS @ 156.25 MHz <sup>4</sup>                                    | —   | 15  | 17  | mA   |

|                                                                |                                              | 1.8 V LVCMOS @ 156.25 MHz <sup>4</sup>                                    | —   | 11  | 22  | mA   |

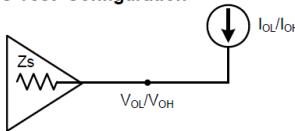

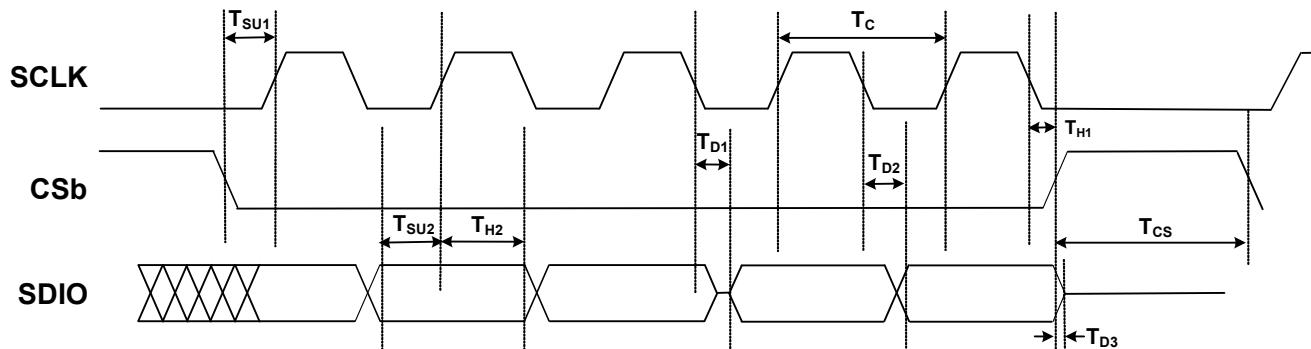

|                                                                |                                              | HCSL internal termination (1.8 V, 2.5 V, 3.3 V) @ 156.25 MHz <sup>5</sup> | —   | 20  | 23  | mA   |