**SKYWORKS®**

DATA SHEET

# SKY66403-11: 2.4 GHz Front-End Module for Zigbee® Technology and Thread/Bluetooth® Applications

## Applications

- In-home appliances

- Smart thermostats

- Internet of Things (IoT) devices

- Smart lighting

- Sensors

- Range extender

- Wireless audio

## Features

- Integrated PA with up to +21 dBm output power

- Integrated LNA (2 dB noise figure typical) and bypass path

- Integrated antenna diversity switching for all modes

- Single-ended transmit/receive interface

- Fast switch on/off time: < 800 ns

- Supply range: 1.8 V to 3.6 V

- Sleep mode current: < 1  $\mu$ A typical

- No external bias resistor required

- Small MCM (22-pin, 3.5 mm x 3.0 mm x 1.0 mm) package, NiPdAu-plated

- MSL3, 260 °C per JEDEC-J-STD-020

- For RoHS and other product compliance information, see [Skyworks Certificate of Conformance](#).

## Description

The SKY66403-11 is a high-performance, fully integrated RF front-end module (FEM) designed for Zigbee® technology, Thread, and Bluetooth® signal (including low energy) applications.

The SKY66403-11 is designed for ease of use and maximum flexibility. The device provides an integrated inter-stage matching and harmonic filter, and digital controls compatible with CMOS levels.

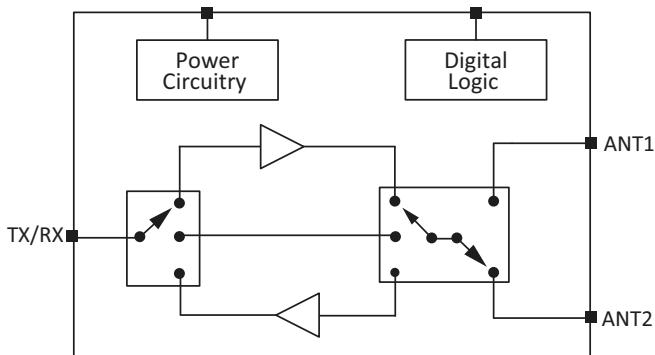

Figure 1. Functional Block Diagram

The RF blocks operate over a wide supply voltage range from 1.8 V to 3.6 V that allows the FEM to be used in battery-powered applications over a wide spectrum of the battery discharge curve.

A functional block diagram is shown in Figure 1. The pin configuration and package are shown in Figure 2. Pin descriptions are provided in Table 1.

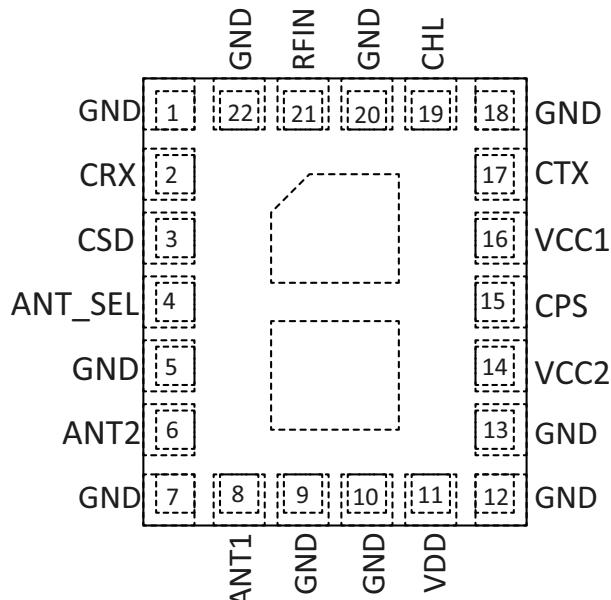

Figure 2. Pinout (Top View)

Table 1. Signal Descriptions

| Pin | Name    | Description                                      | Pin | Name | Description                             |

|-----|---------|--------------------------------------------------|-----|------|-----------------------------------------|

| 1   | GND     | Ground                                           | 12  | GND  | Ground                                  |

| 2   | CRX     | Connect to GPIO signal for mode control          | 13  | GND  | Ground                                  |

| 3   | CSD     | Connect to GPIO signal for mode control          | 14  | VCC2 | PA output stage supply                  |

| 4   | ANT_SEL | Connect to GPIO signal to control antenna switch | 15  | CPS  | Connect to GPIO signal for mode control |

| 5   | GND     | Ground                                           | 16  | VCC1 | PA first stage and LNA supply           |

| 6   | ANT2    | Connect to 50 Ω antenna                          | 17  | CTX  | Connect to GPIO signal for mode control |

| 7   | GND     | Ground                                           | 18  | GND  | Ground                                  |

| 8   | ANT1    | Connect to 50 Ω antenna                          | 19  | CHL  | Connect to GPIO signal for mode control |

| 9   | GND     | Ground                                           | 20  | GND  | Ground                                  |

| 10  | GND     | Ground                                           | 21  | RFIN | RF input power (transmit/receive port)  |

| 11  | VDD     | Digital logic and RF switch supply               | 22  | GND  | Ground                                  |

## Electrical and Mechanical Specifications

The absolute maximum ratings of the SKY66403-11 are provided in Table 2. The recommended operating conditions are specified in Table 3, followed by other electrical specifications and control logic.

**Table 2. Absolute Maximum Ratings<sup>1</sup>**

| Parameter                                                         | Symbol                             | Min                  | Max                  | Units |

|-------------------------------------------------------------------|------------------------------------|----------------------|----------------------|-------|

| Supply voltage                                                    | $V_{CC1}$<br>$V_{CC2}$<br>$V_{DD}$ | -0.3<br>-0.3<br>-0.3 | +3.6<br>+3.6<br>+3.6 | V     |

| Control pin voltage                                               | $V_{CTL}$                          | -0.3                 | +3.6                 | V     |

| Transmit output power at ANT1 or ANT2 port into $50\ \Omega$ load | $P_{OUT\_TX\_MAX}$                 |                      | +22.5                | dBm   |

| Transmit input power at RFIN port                                 | $P_{IN\_TX\_MAX}$                  |                      | +5.0                 | dBm   |

| Receive input power at ANT1 or ANT2 ports <sup>2</sup>            | $P_{IN\_RX\_MAX}$                  |                      | +15                  | dBm   |

| Bypass input power at ANT1 or ANT2 ports <sup>2</sup>             | $P_{IN\_BYP\_MAX}$                 |                      | +20                  | dBm   |

| Operating temperature                                             | $T_A$                              | -40                  | +85                  | °C    |

| Storage temperature                                               | $T_{STG}$                          | -40                  | +125                 | °C    |

| Electrostatic discharge: Human Body Model (HBM)                   | ESD                                |                      | 3000                 | V     |

1. Exposure to maximum rating conditions for extended periods may reduce device reliability. Exceeding any of the limits listed here may result in permanent damage to the device.

2. CW test signal

**ESD Handling:** Industry-standard ESD handling precautions must be adhered to at all times to avoid damage to this device.

**Table 3. Recommended Operating Conditions**

| Parameter                | Symbol    | Min              | Typ | Max | Units |

|--------------------------|-----------|------------------|-----|-----|-------|

| Supply voltage, VCC1 pin | $V_{CC1}$ | 1.7              | 1.8 | 3.6 | V     |

| Supply voltage, VCC2 pin | $V_{CC2}$ | 0.6              | 3.0 | 3.6 | V     |

| Supply voltage, VDD pin  | $V_{DD}$  | 1.8 <sup>1</sup> | 3.0 | 3.6 |       |

| Operating temperature    | $T_C$     | -40              | +25 | +85 | °C    |

1. Performance at  $V_{DD} = 1.8\text{ V}$  will be slightly degraded compared to  $V_{DD} = 2.5\text{ V}$  and above.

**Table 4. Electrical Specifications<sup>1</sup>**

(V<sub>CC1</sub> = 1.8 V, V<sub>CC2</sub> = 3.0 V, V<sub>DD</sub> = 3.0 V, T<sub>A</sub> = +25 °C, Unless Otherwise Noted)

| Parameter                                  | Symbol                             | Test Condition                                                                                                                                                                  | Min       | Typ                  | Max                    | Units |

|--------------------------------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------|------------------------|-------|

| <b>DC Characteristics</b>                  |                                    |                                                                                                                                                                                 |           |                      |                        |       |

| Total supply current                       | I <sub>CC_TX</sub>                 | P <sub>OUT</sub> = +20 dBm, linear<br>P <sub>OUT</sub> = +20 dBm, high-efficiency<br>P <sub>OUT</sub> = +16 dBm, high-efficiency<br>P <sub>OUT</sub> = +13 dBm, high-efficiency |           | 97<br>90<br>60<br>45 |                        | mA    |

| Total supply current                       | I <sub>CC_RX</sub>                 |                                                                                                                                                                                 |           | 3.5                  | 6                      | mA    |

| Total supply current                       | I <sub>CC_BYP</sub>                |                                                                                                                                                                                 |           | 5                    |                        | μA    |

| Sleep supply current                       | I <sub>CC_OFF</sub>                | No RF                                                                                                                                                                           |           |                      | 1                      | μA    |

| Quiescent current                          | I <sub>CCQ_TX</sub>                | Linear mode (CHL high)<br>High-efficiency mode (CHL low)                                                                                                                        |           | 35<br>15             |                        | mA    |

| <b>Logic Characteristics</b>               |                                    |                                                                                                                                                                                 |           |                      |                        |       |

| Control voltage<br>High<br>Low             | V <sub>IH</sub><br>V <sub>IL</sub> |                                                                                                                                                                                 | 1.08<br>0 |                      | V <sub>DD</sub><br>0.3 | V     |

| Control current<br>High<br>Low             | I <sub>IH</sub><br>I <sub>IL</sub> |                                                                                                                                                                                 |           |                      | 1.0<br>1.0             | μA    |

| <b>Dual Antenna Switch Characteristics</b> |                                    |                                                                                                                                                                                 |           |                      |                        |       |

| Isolation between ANT1 and ANT2 ports      | I <sub>SOANTSW</sub>               |                                                                                                                                                                                 |           | -20                  |                        | dB    |

| ANT1 to ANT2 switching time                | t <sub>ANT1_ANT2</sub>             |                                                                                                                                                                                 |           | 400                  |                        | ns    |

1. Performance is assured only under the conditions listed in this table.

**Table 5. Electrical Specifications<sup>1</sup>**(V<sub>CC1</sub> = 1.8 V, V<sub>CC2</sub> = 3.0 V, V<sub>DD</sub> = 3.0 V, T<sub>A</sub> = +25 °C, All Unused Ports Terminated with 50 Ω Unless Otherwise Noted)

| Parameter                               | Symbol            | Test Condition                                                                                                                         | Min                                                   | Typ                      | Max  | Units   |

|-----------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------|------|---------|

| <b>Transmit Characteristics</b>         |                   |                                                                                                                                        |                                                       |                          |      |         |

| Frequency range                         | f                 |                                                                                                                                        | 2400                                                  |                          | 2483 | MHz     |

| Output power at ANT1 or ANT2 port       | POUT              | Linear mode<br>High-efficiency mode<br>High-efficiency mode V <sub>CC2</sub> = 1.8 V<br>High-efficiency mode, V <sub>CC2</sub> = 1.2 V |                                                       | +20<br>+20<br>+16<br>+13 |      | dBm     |

| Saturated gain                          | G <sub>SAT</sub>  | PIN = -2 dBm, linear mode                                                                                                              |                                                       | 22                       |      | dB      |

| Small signal gain                       | S21               | Linear mode                                                                                                                            |                                                       | 22                       |      | dB      |

| Saturated output power variation        | DPOUT             | Across all Zigbee technology application channels                                                                                      |                                                       |                          | 1    | dBp-p   |

| Second and third harmonics <sup>2</sup> | 2fo, 3fo          | POUT = +20.0 dBm, IEEE 802.15.4 source                                                                                                 |                                                       |                          | -42  | dBm/MHz |

| Input return loss                       | S11               |                                                                                                                                        |                                                       | -12                      |      | dB      |

| Turn-on time <sup>2</sup>               | t <sub>RISE</sub> | From 50% of CTX edge to 90% of final RF output power                                                                                   |                                                       | 800                      |      | ns      |

| Turn-off time <sup>2</sup>              | t <sub>FALL</sub> | From 50% of CTX edge to 10% of final RF output power                                                                                   |                                                       | 800                      |      | ns      |

| Stability <sup>2</sup>                  | STAB              | CW, P <sub>IN</sub> = 0 dBm, 0.1 GHz to 20 GHz, load VSWR = 6:1                                                                        | All non-harmonically related outputs<br>< -42 dBm/MHz |                          |      |         |

| Ruggedness <sup>2</sup>                 | RUG               | CW, P <sub>IN</sub> = 0 dBm, load VSWR = 10:1                                                                                          | No permanent damage                                   |                          |      |         |

| <b>Receive Characteristics</b>          |                   |                                                                                                                                        |                                                       |                          |      |         |

| Frequency range                         | f                 |                                                                                                                                        | 2400                                                  |                          | 2483 | MHz     |

| Receive gain                            | RX_GAIN           |                                                                                                                                        |                                                       | 11                       |      | dB      |

| Receive noise figure                    | NF                |                                                                                                                                        |                                                       | 2                        |      | dB      |

| Third order input intercept point       | IIP3              |                                                                                                                                        |                                                       | 2                        |      | dBm     |

| 1 dB input compression point            | IP1dB             |                                                                                                                                        | -14                                                   | -8                       |      | dBm     |

| Input return loss                       | S11               | ANT1 or ANT2 ports                                                                                                                     |                                                       | -10                      |      | dB      |

| Output return loss                      | S22               |                                                                                                                                        |                                                       | -10                      |      | dB      |

| Turn-on time <sup>2</sup>               | t <sub>RISE</sub> | From 50% of CRX edge to 90% of final RF output power                                                                                   |                                                       | 800                      |      | ns      |

| Turn-off time <sup>2</sup>              | t <sub>FALL</sub> | From 50% of CRX edge to 10% of final RF output power                                                                                   |                                                       | 800                      |      | ns      |

| <b>Bypass Characteristics</b>           |                   |                                                                                                                                        |                                                       |                          |      |         |

| Frequency range                         | f                 |                                                                                                                                        | 2400                                                  |                          | 2483 | MHz     |

| Bypass gain                             | BYP_GAIN          |                                                                                                                                        |                                                       | -2                       |      | dB      |

| Input return loss                       | S11               |                                                                                                                                        |                                                       | -15                      |      | dB      |

| Output return loss                      | S22               |                                                                                                                                        |                                                       | -20                      |      | dB      |

1. Performance is assured only under the conditions listed in this table.

2. Not tested in production. Fully characterized and assured by design.

**Table 6. Mode Control Logic<sup>1</sup>**

( $V_{CC1} = 1.8$  V,  $V_{CC2} = 3.0$  V,  $V_{DD} = 3.0$  V,  $T_A = +25$  °C)

| Mode | Description                       | CSD (Pin 3) | CPS (Pin 15) | CRX (Pin 2) | CTX (Pin 17) | CHL (Pin 19) |

|------|-----------------------------------|-------------|--------------|-------------|--------------|--------------|

| 0    | All off (sleep mode) <sup>1</sup> | 0           | X            | X           | X            | X            |

| 1    | Receive LNA mode                  | 1           | 0            | 1           | 0            | X            |

| 2    | Transmit linear mode              | 1           | 0            | X           | 1            | 1            |

| 3    | Transmit high-efficiency mode     | 1           | 0            | X           | 1            | 0            |

| 4    | Receive bypass mode               | 1           | 1            | 1           | 0            | X            |

| 5    | Transmit bypass mode              | 1           | 1            | X           | 1            | X            |

| 6    | All off (sleep mode)              | 1           | X            | 0           | 0            | X            |

1. All controls must be at  $V_{DD}$  or 0 V to achieve the specified sleep current.

**Table 7. Antenna Select Logic**

( $V_{CC1} = 1.8$  V,  $V_{CC2} = 3.0$  V,  $V_{DD} = 3.0$  V,  $T_A = +25$  °C)

| Description       | ANT_SEL (Pin 4) |

|-------------------|-----------------|

| ANT1 port enabled | 0               |

| ANT2 port enabled | 1               |

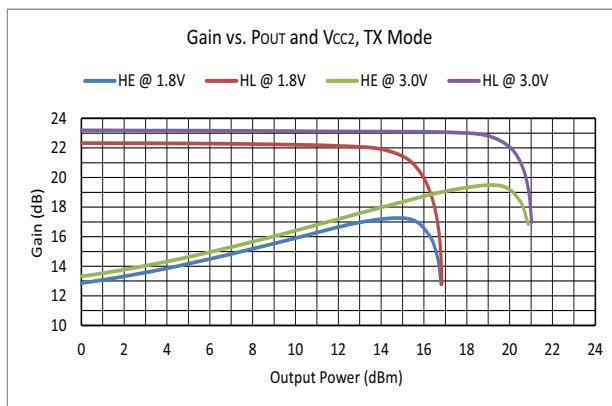

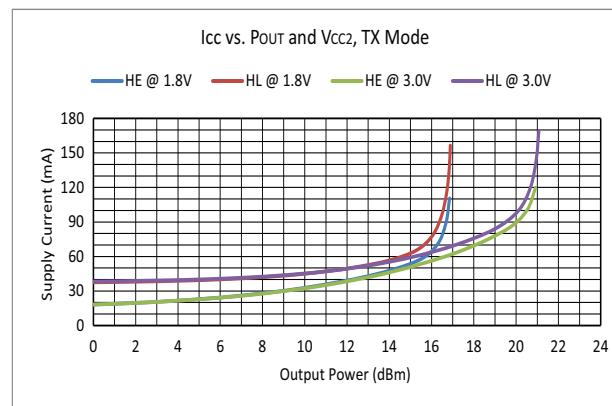

## CHL Control Pin

The CHL pin controls the PA bias.

Use CHL high for high-linearity (HL) mode, which features higher and flat gain vs.  $P_{IN}$ .

Use CHL low for high-efficiency (HE) mode, which features slightly lower  $I_{CC}$  for a given  $P_{OUT}$ .

Due to ACP requirements, high linearity operating modes for enhanced data rate applications must be used.

**Figure 3. Effect of CHL on Gain**

( $V_{CC1} = 1.8$  V,  $V_{DD} = 3.0$  V,  $f = 2440$  MHz)

**Figure 4. Effect of CHL on Supply Current**

( $V_{CC1} = 1.8$  V,  $V_{DD} = 3.0$  V,  $f = 2440$  MHz)

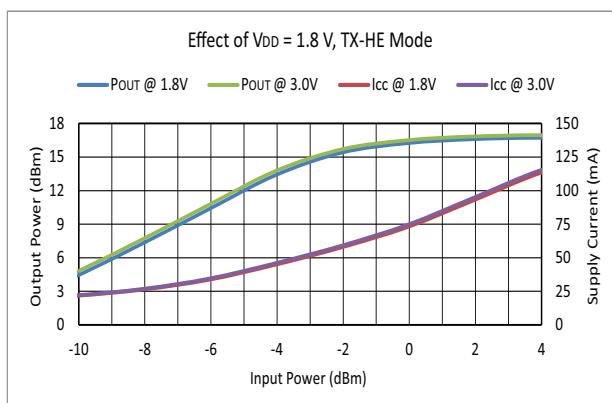

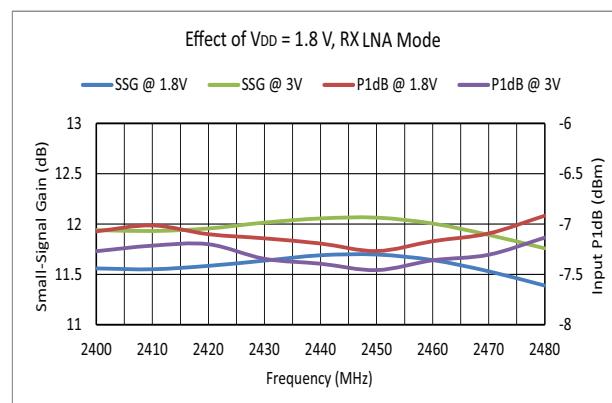

## Effect of $V_{DD}$

$V_{DD}$  supplies the digital logic and the RF switches. It has a nominal level of 3.0 V and typically draws 5 to 20  $\mu$ A in TX, RX, and bypass modes.

Lowering  $V_{DD}$  to 1.8 V reduces TX gain by approximately 0.25 dB and RX gain by about 0.4 dB, but improves RX P1dB by about 0.2 dB.

**Figure 5. Effect of Lowering VDD**

( $V_{CC1} = V_{CC2} = 1.8$  V, TX-HE mode,  $f = 2440$  MHz)

**Figure 6. Effect of Lowering VDD**

( $V_{CC1} = V_{CC2} = 1.8$  V,  $PIN = -25$  dBm, RX-LNA Mode)

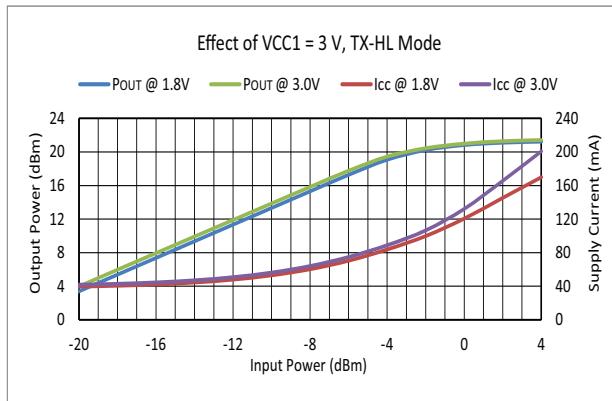

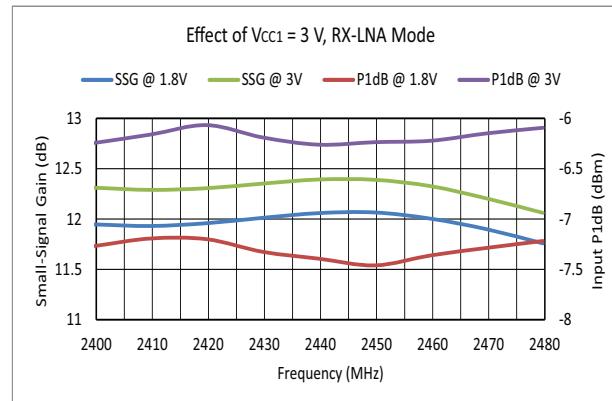

## Effect of $V_{CC1}$

$V_{CC1}$  supplies the LNA and the first stage of the PA. It has a nominal level of 1.8 V and typically draws 10 to 20 mA in TX mode and 3.5 mA in RX mode.

Raising  $V_{CC1}$  to 3.0 V increases RX and TX small-signal gain by about 0.3 dB and RX P1dB by about 1 dB. However, it also increases TX  $I_{CC}$  by 1 to 30 mA depending on input power.

Keep  $P_{IN}$  at or below  $-2$  dBm to prevent high TX  $I_{CC}$ .

Figure 7. Effect of Raising  $V_{CC1}$

( $V_{CC2} = V_{DD} = 3.0$  V,  $f = 2440$  MHz, TX-HL Mode)

Figure 8. Effect of Raising  $V_{CC1}$

( $V_{CC2} = V_{DD} = 3.0$  V,  $P_{IN} = -25$  dBm, RX-LNA Mode)

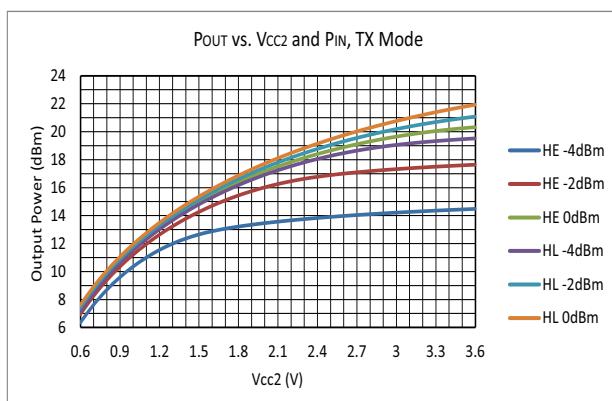

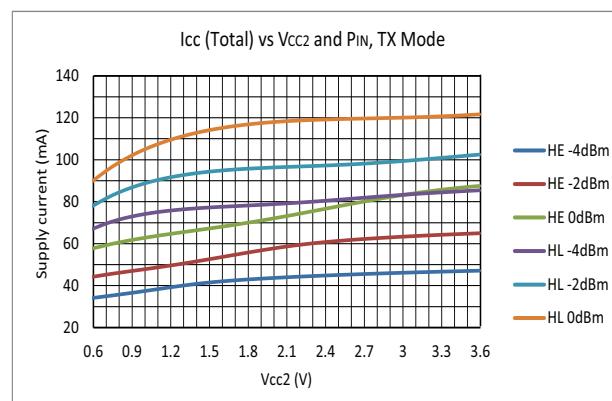

## Effect of $V_{CC2}$

$V_{CC2}$  supplies the output stage of the PA. The level of  $V_{CC2}$  directly controls the saturated TX output power and this supply draws the majority of the current in TX mode.

Figure 9.  $P_{OUT}$  vs.  $V_{CC2}$  and  $P_{IN}$

( $V_{CC1} = 1.8$  V,  $V_{DD} = 3.0$  V,  $f = 2440$  MHz)

Figure 10.  $I_{CC}$  vs.  $V_{CC2}$  and  $P_{IN}$

( $V_{CC1} = 1.8$  V,  $V_{DD} = 3.0$  V,  $f = 2440$  MHz)

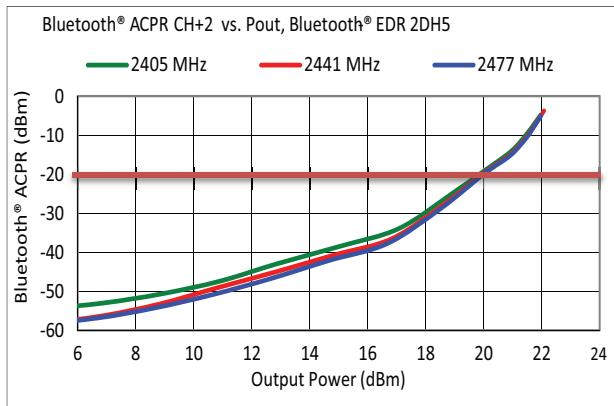

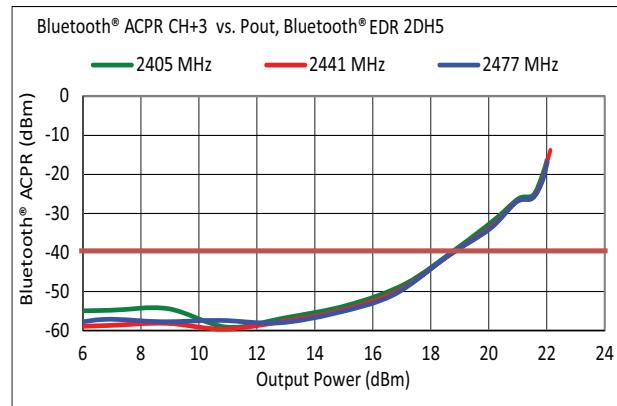

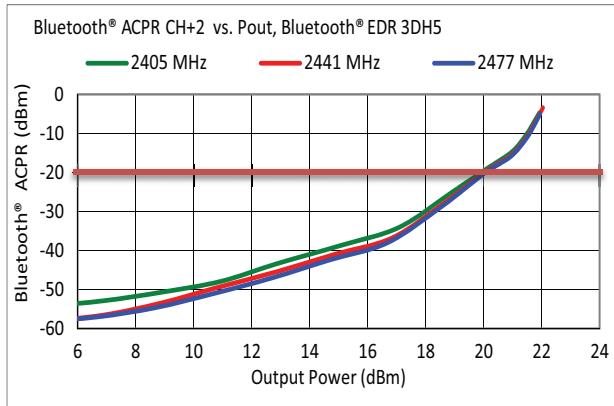

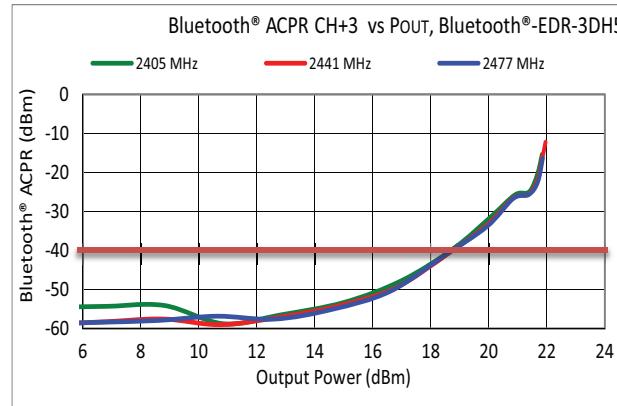

## Adjacent Channel Power for Bluetooth® EDR Applications

The SKY66403-11 in high-linearity (HL) mode benefits from excellent adjacent channel power (ACP) performance in Bluetooth® enhanced data rate applications.

Typical ACP measurements for both enhanced data rate modulations ( $\pi/4$ -DQPSK with 2-DH5 packets and 8-DPSK with 3-DH5 packets) are shown in Figures 11 through 14.

Figure 11. ACPR CH+2 vs  $P_{OUT}$  ( $\pi/4$ -DQPSK with 2-DH5 Packets)

Figure 12. ACPR CH+3 vs  $P_{OUT}$  ( $\pi/4$ -DQPSK with 2-DH5 Packets)

Figure 13. ACPR CH+3 vs  $P_{OUT}$  (8-DPSK with 3-DH5 Packets)

Figure 14. ACPR CH+2 vs  $P_{OUT}$  (8-DPSK with 3-DH5 Packets)

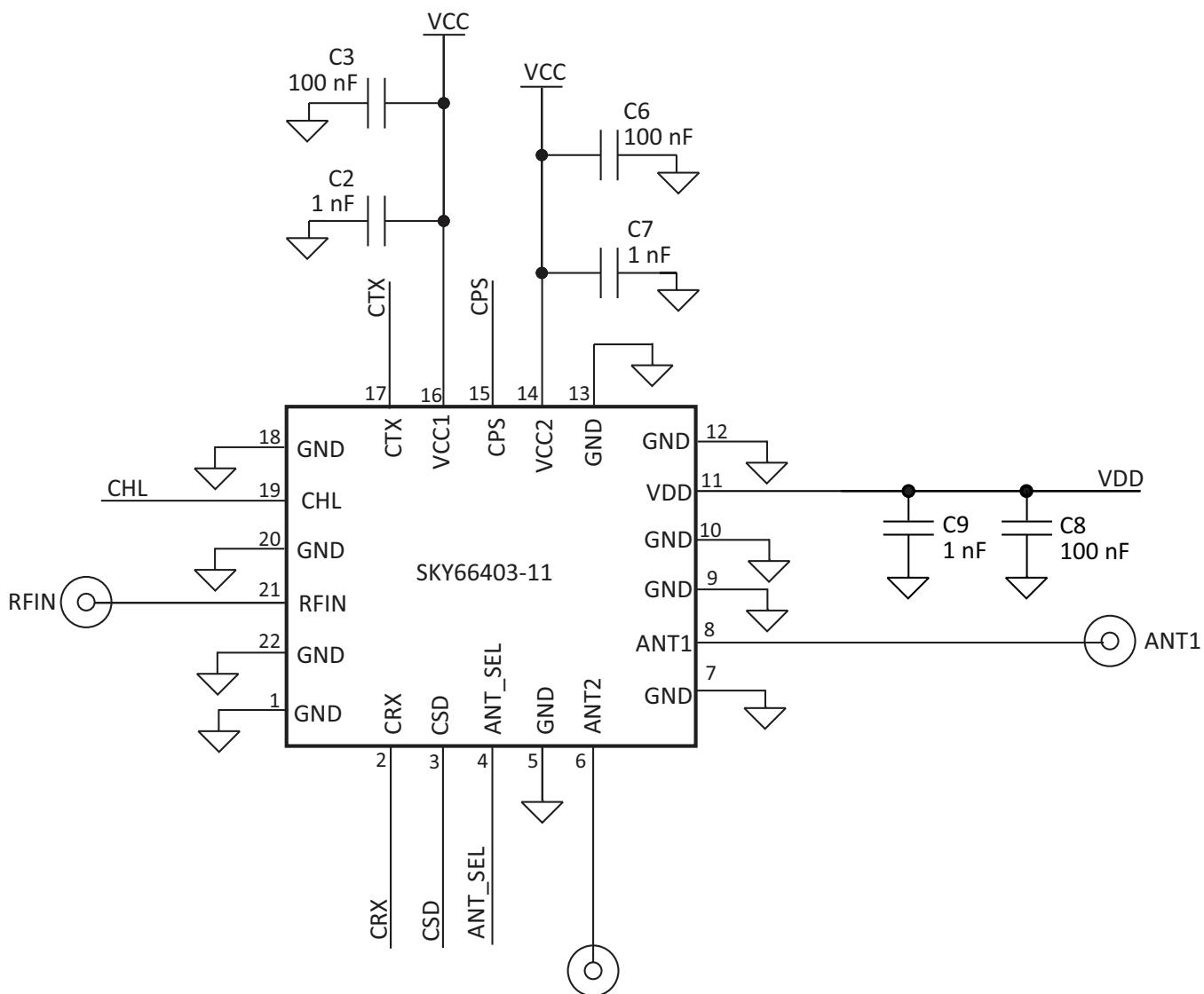

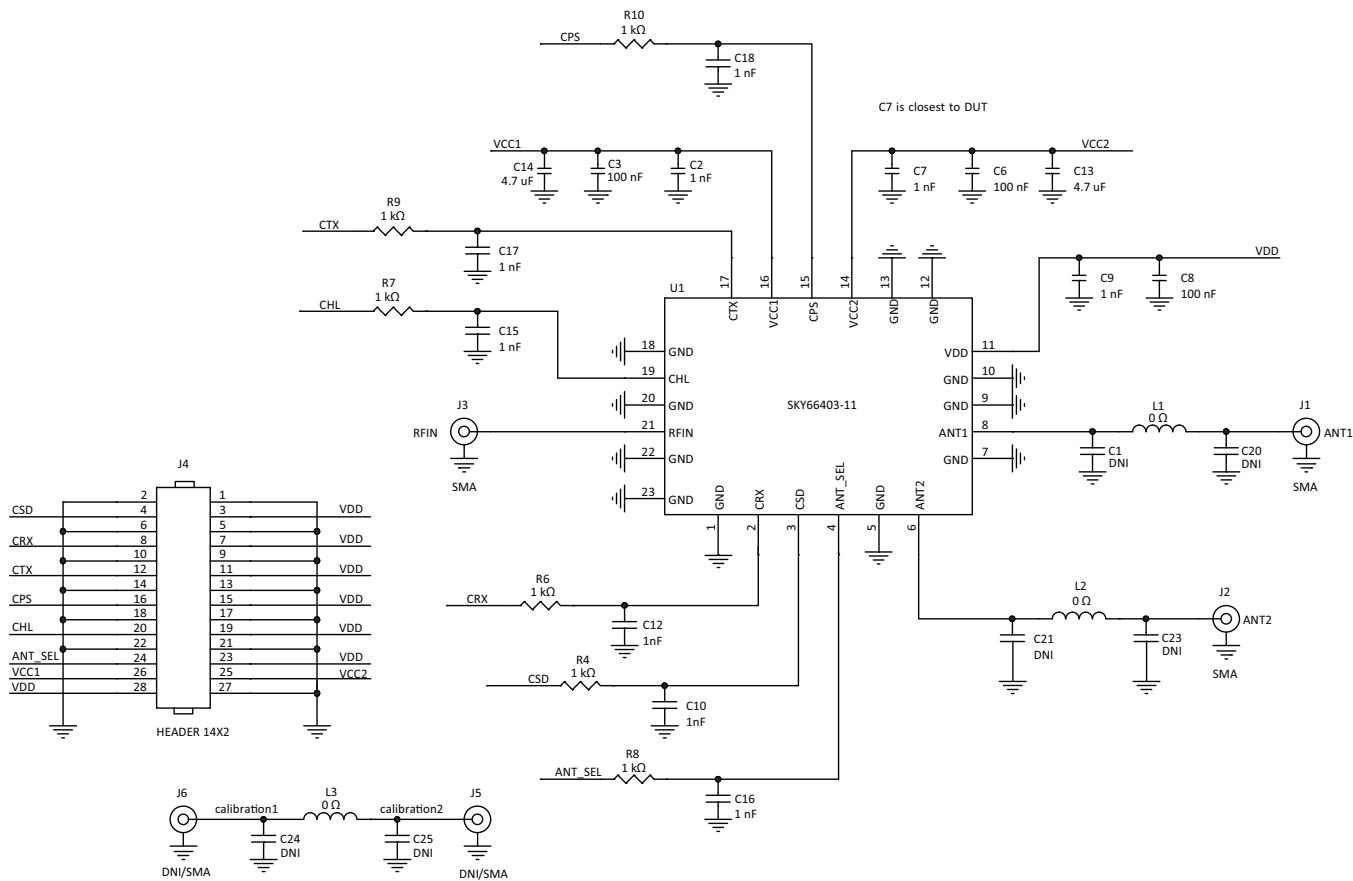

## Reference Design Schematic

A reference design schematic is shown below, and an evaluation board schematic is shown in Figure 16.

Note: The paddle should be connected to ground.

Figure 15. Reference Design Schematic

Figure 16. Evaluation Board Schematic Diagram

## Package and Handling Information

Since the device is sensitive to moisture absorption, it is baked and vacuum packed before shipping. Instructions on the shipping container label regarding exposure to moisture after the container seal is broken must be followed. Otherwise, problems related to moisture absorption may occur when the part is subjected to high temperature during solder assembly.

The SKY66403-11 is rated to Moisture Sensitivity Level 3 (MSL3) at 260 °C. It can be used for lead- or lead-free soldering. For additional information, refer to the Skyworks Application Note, "PCB Design & SMT Assembly Rework Guidelines for MCM-L Packages," document number 101752.

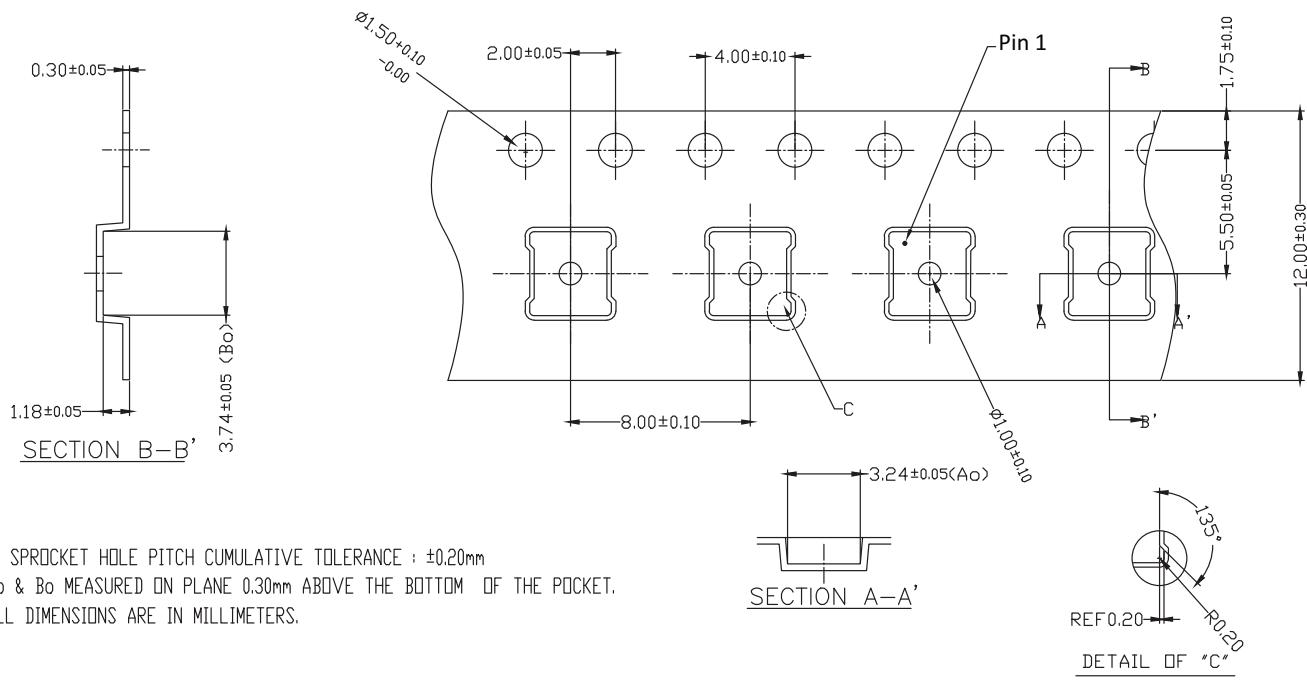

Care must be taken when attaching this product, whether it is done manually or in a production solder reflow environment. Production quantities of this product are shipped in a standard tape and reel format.

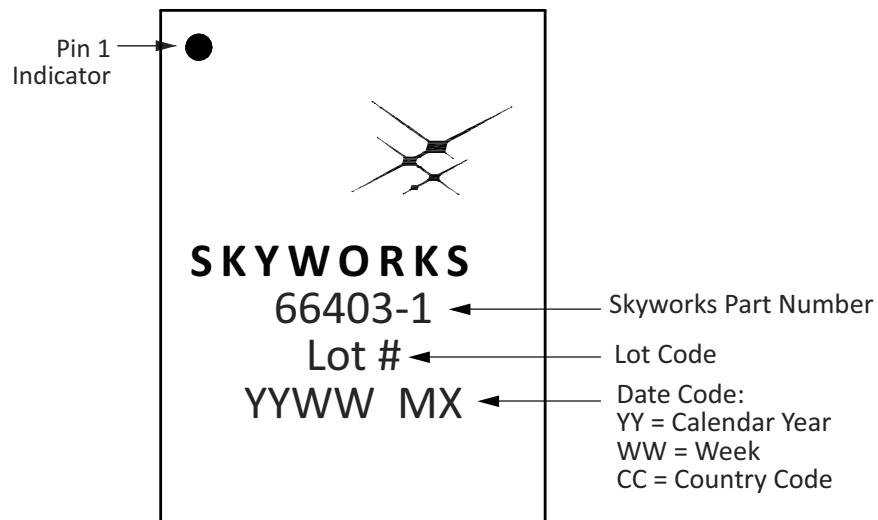

Figure 17. Typical Part Marking

## Notes:

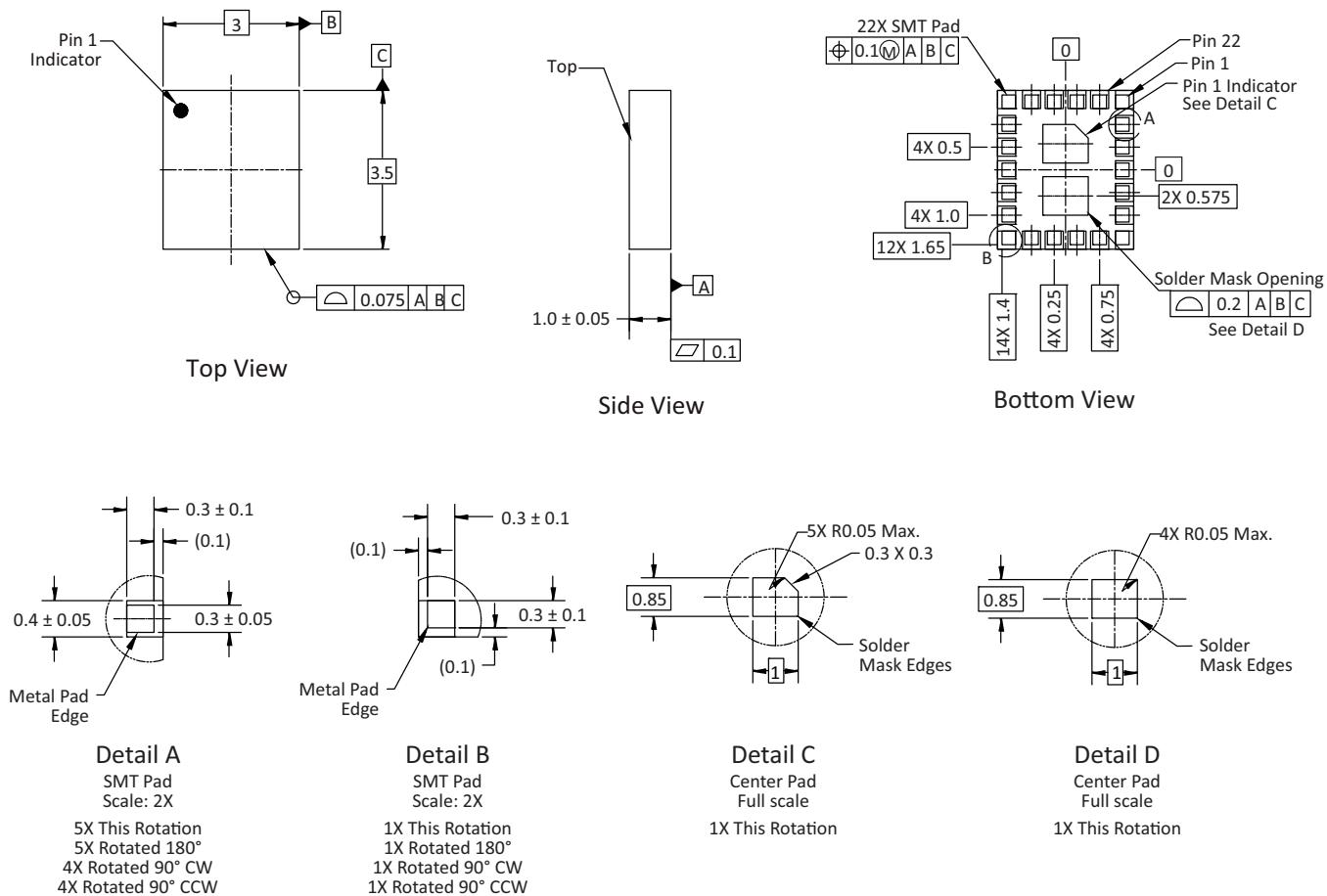

1. Dimensions and tolerances according to ASME Y14.5M-1994.

2. All measurements are in millimeters.

Figure 18. Package Dimensions

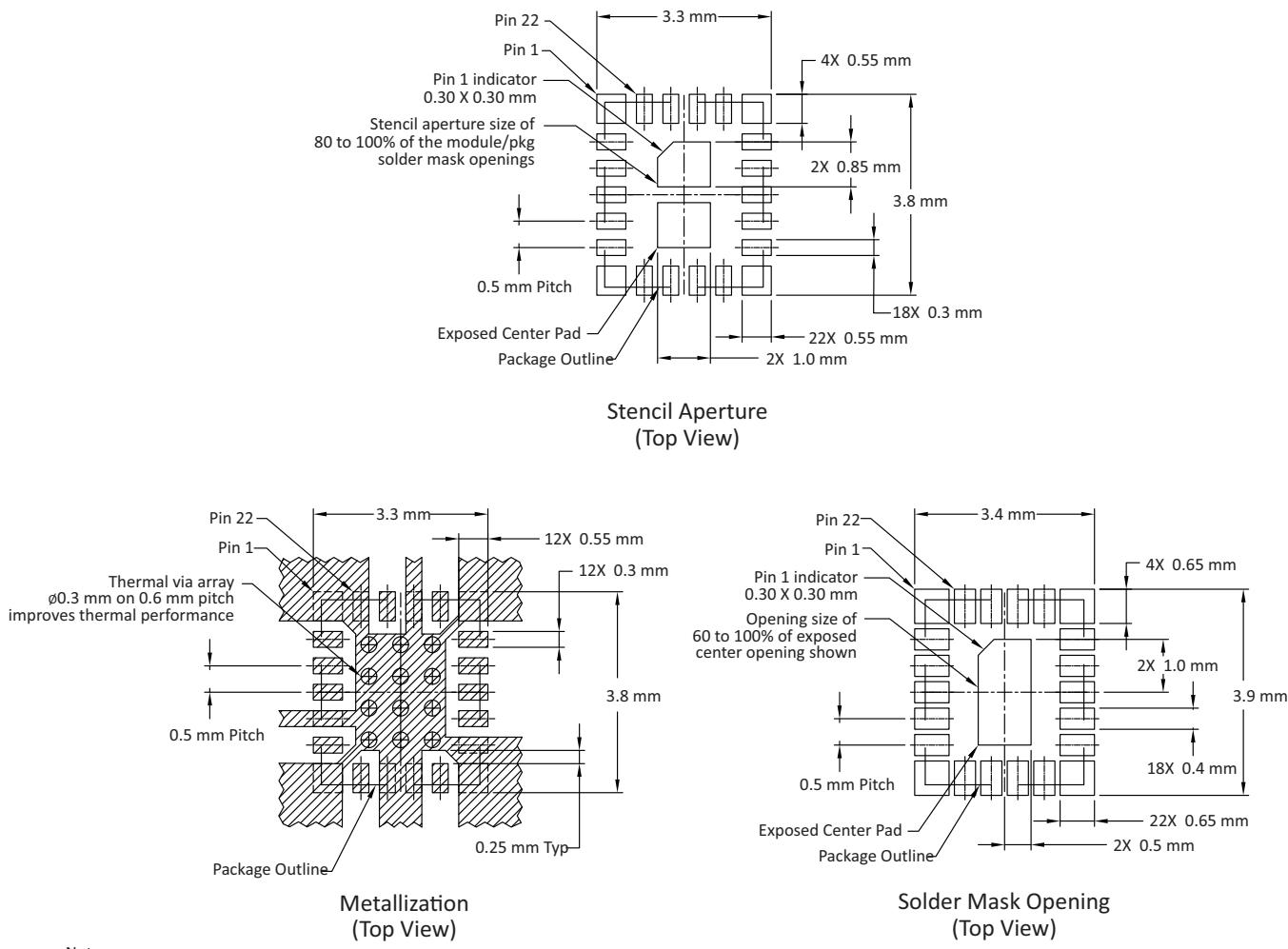

## Note:

1. All measurements are in millimeters.

2. Thermal vias should be resin filled and capped in accordance with IPC-4761 type VII vias. Recommended Cu thickness is 30 to 35  $\mu$ m.

Figure 19. PCB Layout Footprint

Figure 20. Tape and Reel Information

## Ordering Information

| Part Number | Description                                                                        | Evaluation Board Part Number |

|-------------|------------------------------------------------------------------------------------|------------------------------|

| SKY66403-11 | 2.4 GHz Front-End Module for Zigbee® Technology and Thread/Bluetooth® Applications | SKY66403-11EK1               |

Copyright © 2016-2017, 2022-2023, 2025, Skyworks Solutions, Inc. All Rights Reserved.

Information in this document is provided in connection with Skyworks Solutions, Inc., and its subsidiaries ("Skyworks") products or services. These materials, including the information contained herein, are provided by Skyworks as a service to its customers and may be used for informational purposes only by the customer. Skyworks assumes no responsibility for errors or omissions in these materials or the information contained herein. Skyworks may change its documentation, products, services, specifications or product descriptions at any time, without notice. Skyworks makes no commitment to update the materials or information and shall have no responsibility whatsoever for conflicts, incompatibilities, or other difficulties arising from any future changes.

No license, whether express, implied, by estoppel or otherwise, is granted to any intellectual property rights by this document. Skyworks assumes no liability for any materials, products or information provided hereunder, including the sale, distribution, reproduction or use of Skyworks products, information or materials, except as may be provided in Skyworks' Terms and Conditions of Sale.

THE INFORMATION IN THIS DOCUMENT AND THE MATERIALS AND PRODUCTS DESCRIBED THEREIN ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, WHETHER EXPRESS, IMPLIED, STATUTORY, OR OTHERWISE, INCLUDING FITNESS FOR A PARTICULAR PURPOSE OR USE, MERCHANTABILITY, PERFORMANCE, QUALITY OR NON-INFRINGEMENT OF ANY INTELLECTUAL PROPERTY RIGHT; ALL SUCH WARRANTIES ARE HEREBY EXPRESSLY DISCLAIMED. SKYWORKS DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. SKYWORKS SHALL NOT BE LIABLE FOR ANY DAMAGES, INCLUDING BUT NOT LIMITED TO ANY SPECIAL, INDIRECT, INCIDENTAL, STATUTORY, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS THAT MAY RESULT FROM THE USE OF THE MATERIALS OR INFORMATION, WHETHER OR NOT THE RECIPIENT OF MATERIALS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

Skyworks products are not designed, intended, authorized, or warranted for use or inclusion in life support or life endangering applications, devices, or systems where failure or inaccuracy might cause death or personal injury. Skyworks customers agree not to use or sell the Skyworks products for such applications, and further agree to, without limitation, fully defend, indemnify, and hold harmless Skyworks and its agents from and against any and all actions, suits, proceedings, costs, expenses, damages, and liabilities including attorneys' fees arising out of or in connection with such improper use or sale.

Skyworks assumes no liability for applications assistance, customer product design, or damage to any equipment resulting from the use of Skyworks products outside of Skyworks' published specifications or parameters. Customers are solely responsible for their products and applications using the Skyworks products.

"Skyworks" and the Skyworks Starburst logo are registered trademarks of Skyworks Solutions, Inc., in the United States and other countries. Third-party brands and names are for identification purposes only and are the property of their respective owners. Additional information, including relevant terms and conditions, posted at [www.skyworksinc.com](http://www.skyworksinc.com), are incorporated by reference.